# Polynomial Multiplication for Post-Quantum Cryptography

Cover design: @WinloxArts with Jonalyn Madriaga and Felix Wilhelm Printed by GVO drukkers & vormgevers

This work has been supported by the European Commission through the ERC Starting Grant 805031 (EPOQUE).

No rights reserved

# Polynomial Multiplication for Post-Quantum Cryptography

#### Proefschrift

ter verkrijging van de graad van doctor aan de Radboud Universiteit Nijmegen op gezag van de rector magnificus prof. dr. J.H.J.M. van Krieken, volgens besluit van het college voor promoties in het openbaar te verdedigen op

> maandag 4 april 2022 om 12:30 uur precies

> > door

Matthias Julius Kannwischer

geboren op 20 april 1993 te Tübingen, Duitsland

#### Promotoren:

prof. dr. Peter Schwabe prof. dr. Bo-Yin Yang Academia Sinica, Taiwan

### Manuscriptcommissie:

prof. dr. Lejla Batina (voorzitter)

prof. dr. Daniel J. Bernstein University of Illinois Chicago, Verenigde Staten en Ruhr-Universität Bochum, Duitsland

prof. dr. ing. Tim Güneysu Ruhr-Universität Bochum, Duitsland

prof. dr. ir. Ingrid Verbauwhede Katholieke Universiteit Leuven, België

dr. Joppe W. Bos $NXP\ Semiconductors,\ Belgi\ddot{e}$

## Acknowledgements

First and foremost, I want to thank Peter Schwabe for supervising me over the last few years. From the moment we met in Tenerife, you supported me in my research and always made time for me when I asked for advice. I admire your positive attitude to virtually everything which helped me a lot to get through the frustrating phases of my PhD. I am very grateful that you allowed and encouraged me to attend numerous academically valuable conferences, workshops, and schools in many touristically valuable places. Thank you, Peter!

I also want to thank my second supervisor Bo-Yin Yang. You intended to invite me for a 6-week research visit to Taipei in March 2020. Now, two years later, I am still here. Thank you for jumping through all the hoops to allow me to stay and come back! I am also honored that you agreed to be my second supervisor and I enjoyed the many technical and non-technical discussions we had. And Sukiyaki! Also, thanks to your assistant Sinman who helped me with a lot of Mandarin paperwork and supplied me with food during my first quarantine.

I also want to thank my previous supervisor at the University of Surrey, Liqun Chen. You introduced me to cryptography when I was working at HP Labs in 2014, and encouraged me to pursue a PhD. Without you, I would not be where I am today!

I thank the members of my reading committee Lejla Batina, Daniel J. Bernstein, Joppe W. Bos, Tim Güneysu, and Ingrid Verbauwhede for taking the time to read this thesis and providing me valuable feedback.

Even though there is one name on this book, this is the result of collaborations with numerous people. It was great fun to be able to work with so many different people from around the world. Thank you to my co-authors Albrecht, Amin, Andreas, Andrew, Aymeric, Bo-Yin, Cheng-Jhih, Daan, Denis, Denisa, Dieter, Elisabeth, Fabio, Gregor, Hanno, Hervé, Hiroshi, Jacques, Jintai, Jiun-Peng, Johannes, Joost, Juliane, Ko, Leon, Marc, Marvin, Michael, Ming-Shing, Peter, Peter, Robert, Ruben, Shang-Yi, Tanja, Thom, Tung, Vincent, and Yu-Jia.

I thank everyone who has proofread parts of this thesis beforehand. Thanks Amin, Daan, Fabio, Jonathan, Krijn, Lorenz, Pedro, and Thom. I am grateful for having had the opportunity to teach and supervise various students over the years. I enjoyed it very much and you taught me much more than I could ever teach you.

Having worked in four institutes in four countries over the course of my PhD, I have met many great people and made a lot of friends. Thank you for a great time!

Thank you, Dan and Jorden. You introduced me to the PhD student life and British customs. I hope we will go to Greggs soon. Also thanks to François, Ioana, Johnni, and Linda for the great (although brief) time in Guildford.

Thank you to the many great people in Nijmegen. Thanks for coffee breaks, crypto dinners, vrjidag middag borrels, barbeques, and movie nights. In particular, I want to thank Joost, Ko, and Pedro. I appreciated all your help when starting in Nijmegen.

Thanks, Pedro, for still advising me today about the problems of life and Montgomery multiplications.

I moved flats many times in the last years, but only once did I move flats while physically being on the other end of the world. Thank you, Loes, Joost, Veelasha, and Peter for supporting this crazy endeavor.

For my time in Bochum, I want to thank Irmgard for helping me a great lot with paperwork. Thank you, Nils, for generously offering to supply me with food during yet another involuntary quarantine.

I thank Dor, Lorenz, and Jonathan for sharing an office with me in Taipei and exploring this exceptionally beautiful country. Thank you, Dan and Tanja, for the many nice hot pot dinners.

Thanks, Fabio, for your support and helping me to accept that even my code sometimes contains bugs.

I want to thank my friends at home. Even though my decision to move abroad meant I could not see you very often, it is great to not be forgotten. Thank you for thinking of me, staying in touch, and for making me feel welcome when I was visiting home. In particular, I want to thank Anna, Felix, Martin, Max, Michael, Paul, Sabrina, and Tim.

I thank my family for always supporting me and trying very hard to understand what I am doing in my research. Thanks especially to my parents, Bärbel and Helmut, for always helping and encouraging me! Thank you also to Christian and Thomas for numerous skiing trips and inspiring advice. Thank you, Winfried, for exciting me about science. Thank you, grandma, Karin, Keith, Sabine, too.

Jonalyn, I thank you for making the last two years very special and fun. Thank you, for your patience, support, love, and all the delicious food!

Thank you all.

Matthias Kannwischer Taipei, January 2022

## Contents

| Contents |              |                       |                                                    | vii             |

|----------|--------------|-----------------------|----------------------------------------------------|-----------------|

| 1        | Int          | roduct                | ion                                                | 1               |

|          | 1.1          |                       | ibutions                                           | 6               |

| <b>2</b> | Dro          | limina                | rios                                               | 11              |

| 4        | 2.1          |                       | ographic Schemes                                   | 11              |

|          | 2.1          | 2.1.1                 | Key-Establishment Schemes                          | 11              |

|          |              | 2.1.1 $2.1.2$         | Digital Signature Schemes                          | 13              |

|          | 2.2          |                       | omial Multiplication for Computer Scientists       | $\frac{13}{14}$ |

|          | 2.2          | 2.2.1                 | Schoolbook Multiplication                          | $\frac{14}{17}$ |

|          |              | $\frac{2.2.1}{2.2.2}$ | <u>-</u>                                           | 19              |

|          |              | 2.2.2                 | Karatsuba Multiplication                           |                 |

|          |              |                       | Toom-Cook Multiplication                           | 20<br>24        |

|          |              | 2.2.4                 | Number-Theoretic Transform (NTT)                   |                 |

|          |              | 2.2.5 $2.2.6$         | Algorithms for Computing NTTs                      | 29<br>34        |

|          |              |                       | Radix-3 FFT and Mixed-Radix FFT                    |                 |

|          |              | 2.2.7                 | Incomplete NTT                                     | 35              |

|          | 0.0          | 2.2.8                 | Good's Trick                                       | 37              |

|          | 2.3          |                       | lar-Reduction Algorithms and Short Multiplications | 39              |

|          |              | 2.3.1                 | Barrett Reduction                                  | 40              |

|          | 0.4          | 2.3.2                 | Montgomery Reduction and Montgomery Multiplication |                 |

|          | 2.4          |                       | Cortex-M3 and Arm Cortex-M4                        | 43              |

|          |              | 2.4.1                 | Arm Cortex-M4                                      | 45              |

|          |              | 2.4.2                 | Arm Cortex-M3                                      | 47              |

|          |              |                       |                                                    |                 |

| Ι        | $\mathbf{M}$ | ultipl                | ication for NTT-friendly Rings                     | <b>49</b>       |

| 3        | Kyb          | er on                 | Cortex-M4                                          | 51              |

|          | 3.1          | Prelin                | ninaries                                           | 52              |

|          |              | 3.1.1                 | Kyber v1                                           | 53              |

|          |              | 3.1.2                 | Kyber v2                                           | 55              |

|          |              | 3.1.3                 | Arm Cortex-M4                                      | 56              |

|          | 3.2          | Optin                 | nizing for Speed                                   | 56              |

|          |              | 3.2.1                 | Link-Time Optimization                             | 56              |

|          |              | 3.2.2                 | Speeding up the NTT                                | 57              |

|    |                                         | 3.2.3  | Optimizing Matrix-Vector Multiplication 59           |  |  |  |

|----|-----------------------------------------|--------|------------------------------------------------------|--|--|--|

|    |                                         | 3.2.4  | Optimized Keccak                                     |  |  |  |

|    |                                         | 3.2.5  | Kyber v2                                             |  |  |  |

|    | 3.3                                     |        | asing Stack Usage                                    |  |  |  |

|    | 3.4                                     |        | ts                                                   |  |  |  |

|    |                                         | 3.4.1  | NTT and Polynomial Multiplication 63                 |  |  |  |

|    |                                         | 3.4.2  | Kyber.CCA                                            |  |  |  |

|    |                                         | 3.4.3  | Profiling                                            |  |  |  |

|    |                                         | 3.4.4  | Comparison to other PQC Schemes 68                   |  |  |  |

| 4  | Dilithium on Cortex-M3 and Cortex-M4 69 |        |                                                      |  |  |  |

|    | 4.1                                     |        | ninaries                                             |  |  |  |

|    |                                         | 4.1.1  | Dilithium                                            |  |  |  |

|    |                                         | 4.1.2  | Target Platforms: Cortex-M3 and Cortex-M4 74         |  |  |  |

|    | 4.2                                     | Impro  | ving Cortex-M4 Performance                           |  |  |  |

|    | 4.3                                     | _      | Constant-Time NTTs on Cortex-M3                      |  |  |  |

|    |                                         | 4.3.1  | smull and smlal 79                                   |  |  |  |

|    |                                         | 4.3.2  | Cooley–Tukey and Gentleman–Sande Butterflies 8       |  |  |  |

|    |                                         | 4.3.3  | $NTT$ , $NTT^{-1}$ , and $\circ$ 82                  |  |  |  |

|    | 4.4                                     | Time-  | Memory Trade-Offs                                    |  |  |  |

|    |                                         | 4.4.1  | Strategy 1: A in Flash 84                            |  |  |  |

|    |                                         | 4.4.2  | Strategy 2: A in SRAM 84                             |  |  |  |

|    |                                         | 4.4.3  | Strategy 3: Streaming A and y 8                      |  |  |  |

|    |                                         | 4.4.4  | Splitting Signature Generation in an Offline and On- |  |  |  |

|    |                                         | D 1    | line Phase                                           |  |  |  |

|    | 4.5                                     |        | S                                                    |  |  |  |

|    |                                         | 4.5.1  | NTT Performance                                      |  |  |  |

|    |                                         | 4.5.2  | Cortex-M4 Performance                                |  |  |  |

|    |                                         | 4.5.3  | Cortex-M3 Performance                                |  |  |  |

|    |                                         | 4.5.4  | Stack Usage                                          |  |  |  |

|    | 1 C                                     | 4.5.5  | Profiling                                            |  |  |  |

|    | 4.6                                     | Nyber  | and NewHope on Cortex-M3 90                          |  |  |  |

|    |                                         |        |                                                      |  |  |  |

| II | $\mathbf{N}$                            | Iultip | lication for NTT-unfriendly Rings 93                 |  |  |  |

| 5  | Too                                     | m–Co   | ok and Karatsuba for NISTPQC 99                      |  |  |  |

| -  |                                         |        | ninaries                                             |  |  |  |

|    |                                         | 5.1.1  | Cryptosystems Optimized in this Chapter 9'           |  |  |  |

|    |                                         | 5.1.2  | Arm Cortex-M4                                        |  |  |  |

|    | 5.2                                     |        | polication in $\mathbb{Z}_{2^m}[x]$                  |  |  |  |

|    |                                         | 5.2.1  | Toom/Karatsuba Strategies                            |  |  |  |

|    |                                         | 5.2.2  | Small Schoolbook Multiplications 100                 |  |  |  |

|    | 5.3                                     |        | rs and Discussion 10'                                |  |  |  |

|              |                  | 5.3.1            | Multiplication Results                                        | 108               |  |

|--------------|------------------|------------------|---------------------------------------------------------------|-------------------|--|

|              |                  | 5.3.2            | Encapsulation and Decapsulation Results                       | 112               |  |

|              |                  | 5.3.3            | Profiling of Optimized Implementations                        | 115               |  |

| c            | NITTO            | T. N.C14         | Link 4: f NITT f.: 11 D:                                      | 117               |  |

| 6            | 6.1              |                  | tiplication for NTT-unfriendly Rings                          | 117<br>119        |  |

|              | 0.1              | 6.1.1            |                                                               | 119               |  |

|              |                  | 6.1.1            |                                                               | 119 $120$         |  |

|              | 6.2              |                  | FFT-based Polynomial Multiplications and NTT on the Cortex-M4 | 120               |  |

|              | 0.2              | 6.2.1            |                                                               |                   |  |

|              |                  | 6.2.1            | Saber                                                         | 121               |  |

|              |                  | 6.2.2            | NTRU                                                          | 123               |  |

|              | 6.3              |                  | LAC                                                           | 126<br>127        |  |

|              | 0.5              | 6.3.1            | Fast Mulmods                                                  | $\frac{127}{127}$ |  |

|              |                  | 6.3.2            | Choice of Transforms                                          | 127               |  |

|              |                  | 6.3.2            | Register Allocation                                           | 130               |  |

|              |                  | 6.3.4            | Range Analysis                                                | 131               |  |

|              | 6.4              | Results          |                                                               | 131               |  |

|              | 0.4              | 6.4.1            | Saber Results                                                 | $131 \\ 132$      |  |

|              |                  | 6.4.1            | NTRU Results                                                  | $132 \\ 135$      |  |

|              |                  | 6.4.2            |                                                               | 136               |  |

|              |                  | 0.4.5            | LAC Results                                                   | 190               |  |

| 7            | Rec              | ent De           | evelopments and Outlook                                       | 141               |  |

| Ac           | crony            | $m_{\mathbf{s}}$ |                                                               | 145               |  |

|              |                  |                  |                                                               |                   |  |

| Bi           | bliog            | graphy           |                                                               | 147               |  |

| $\mathbf{A}$ | Res              | earch l          | Data Management                                               | 165               |  |

| Su           | Summary 10       |                  |                                                               |                   |  |

| <b>C</b> -   | ***              |                  |                                                               | 169               |  |

| sa           | Samenvatting 1   |                  |                                                               |                   |  |

| Al           | About the Author |                  |                                                               |                   |  |

## Chapter 1

## Introduction

Protecting means of communication has been a human need since ancient times. With the advancement of public-key cryptography in the 1970s [DH76], secure communication without a shared secret key became feasible for the first time. With the rise of the internet, this technology became widespread and the vast majority of individuals, corporations, and governments rely on public-key cryptography daily.

At the core of any secure communication, we are interested in protecting the confidentiality, integrity, and authenticity of data. Confidentiality refers to the inability of unauthorized parties to read the contents of the exchanged messages. The integrity of messages implies that the receiver can be sure that the message has not been manipulated by a third party. Lastly, authenticity guarantees that a message was transmitted by the claimed sender. Cryptography offers a way to guarantee these security goals using cryptographic schemes. Most commonly, we use encryption for achieving confidentiality, and digital signatures or message-authentication codes (MAC) for achieving integrity and authenticity. We distinguish two categories of cryptographic schemes: symmetric (or secret-key) cryptography and asymmetric (or publickey) schemes. While secret-key cryptography requires both the sender and receiver to share a cryptographic secret (e.g., a long random password) that must not be known by any adversary, public-key cryptography works fundamentally different: One party generates a key pair consisting of a secret key and a public key. The public key is shared with the world (e.g., posted on a website), while the secret key must remain private. In the case of public-key encryption (PKE), it then suffices to be in possession of the public key to encrypt messages which can then only be decrypted by the owner of the secret key. For digital signatures, a message is signed using the secret key and the signature can be verified using the corresponding public key.

However, public-key cryptography is much more costly than secret-key cryptography both in terms of computation time and data that needs to be transmitted. Hence, it is customary to combine public-key cryptography with a secret-key primitive, i.e., encrypt a small symmetric key (e.g., 256 bit) using PKE which is then used to key a symmetric cipher. A public-key scheme that can only be used for encrypting such a short key is referred to as a key-encapsulation mechanism (KEM). A KEM, however, is more general than a fixed-size PKE as it is not necessarily the case that the key can be chosen. It can also be derived as a part of the KEM.

Unfortunately, the advancement of quantum computers threatens the security of public-key cryptography. This is mostly due to Shor's algorithm [Sho94] which was published in 1994. Shor's algorithm allows to factor a large integer into its prime factors on a quantum computer in polynomial time while the best-known classical algorithms require super-polynomial time. Also, Shor's algorithm allows computing discrete logarithms in polynomial time. This has devastating consequences as common public-key schemes rely on the hardness of factoring or computing discrete logarithms: RSA [RSA78] relies on factoring, DH [DH76] relies on the discrete-logarithm problem (DLP), elliptic-curve cryptography (ECC) [Mil85] relies on the elliptic-curve DLP. Once a large-scale quantum computer is available, cryptographic schemes building upon these problems can be broken and it is possible to compute the secret keys from the public keys. Hence, all encrypted messages can be decrypted, and all digital signatures are useless as one can simply forge signatures. Even worse, it is possible to record encrypted messages now and decrypt them using a future quantum computer. Even though large-scale quantum computers are not existing today, recent progress in their development suggests that they might exist in the next decades [MP21].

This motivates the need to migrate away from these schemes based on factoring or the DLP to schemes that resist attacks by both classical computers and also quantum computers. This type of cryptography is called post-quantum cryptography and started attracting interest in the cryptographic research community in the 2000s which resulted in proposals over the last two decades. Cryptography that cannot resist quantum attacks is called classical cryptography in the following. Note that the use of post-quantum cryptography does not require a quantum computer, i.e., it can be deployed on classical computers.

Aside from Shor's algorithm, there is one other noteworthy quantum algorithm that needs to be taken into account: Grover's algorithm [Gro96]. It allows searching a set of size n in  $\sqrt{n}$  steps, a task that would require n steps on a classical computer. This also applies to cryptography: It can be used to search a cryptographic key by enumerating all possible keys (i.e., brute-forcing). This mostly impacts symmetric cryptography as the best-known attacks are often close to brute-forcing. Luckily, this square-root speed-up can be countered by doubling the key sizes. For example, one could use a key length of 256 bits rather than 128 bits when using the Advanced

| family  | KEM/PKE | signature |

|---------|---------|-----------|

| Code    | 18      | 3         |

| Hash    | 0       | 2         |

| Isogeny | 1       | 0         |

| Lattice | 21      | 5         |

| MQ      | 3       | 7         |

| Other   | 6       | 3         |

| Total   | 49      | 20        |

Table 1.1: 69 complete and proper submission to the NISTPQC [NIS16]

Encryption Standard (AES) [DR02] to achieve comparable post-quantum security. Hence, the term post-quantum cryptography commonly refers to quantum-resistant public-key cryptography.

Due to the emerging threat of quantum computers, the US National Institute for Standards and Technology (NIST) has announced in 2016 [NIS16] that it plans to replace their standards based on the DLP and factoring with post-quantum alternatives. Specifically, this affects their standards for key establishment (NISTSP800-56 [Nat18, Nat19a]), and digital signatures (FIPS186-4 [Nat13]). The replacements are to be determined in a public competition for which a call for proposals was published in 2016 with a deadline for submissions in late 2017. We refer to the competition as NISTPQC in the following. Since key-establishment protocols can be built from either public-key encryption algorithms or key-encapsulation algorithms, and, hence, NIST decided to accept submissions for both. In contrast to the previous AES and SHA-3 competitions, NIST does not plan to select a single winner for each category, but expects to select multiple schemes. Therefore, it is sometimes referred to as the NISTPQC project (or not-a-competition) rather than a competition. Similar to previous NIST competitions, NIST aims to standardize multiple parameter sets providing different levels of security. To enable this, NIST defined security levels one to five providing at least the classical and post-quantum security as AES128, SHA256, AES192, SHA384, and AES256, respectively. Most submissions only provide parameter sets that target security levels one, three, and five. NISTPQC consists of multiple rounds of evaluation and at the end of each round, NIST selects a subset of proposals for the next round and publishes a report justifying their selection. NIST received 82 submissions of which it deemed 69 as complete and proper [NIS16]. Among those submissions were all five major families of schemes that are conjectured to resist quantum attacks: code-based cryptography, hash-based cryptography, isogeny-based cryptography, lattice-based cryptography, and multivariate-based cryptography. See Table 1.1 for an overview distribution of the submissions. While they all come with their advantages and disadvantages, all have promising instantiations which may

|         | KEM/PKE                               | signature                                               |

|---------|---------------------------------------|---------------------------------------------------------|

| Code    | BIKE, Classic McEliece,               | _                                                       |

|         | HQC, LEDAcrypt, NTS-                  |                                                         |

|         | KEM, ROLLO, RQC                       |                                                         |

| Hash    | _                                     | SPHINCS <sup>+</sup>                                    |

| Isogeny | SIKE                                  | _                                                       |

| Lattice | FrodoKEM, Kyber, LAC,                 | <b><u>Dilithium</u></b> , <b><u>Falcon</u></b> , qTesla |

|         | NewHope, <u>NTRU</u> , NTRU           |                                                         |

|         | <b>Prime</b> , Round5, <b>Saber</b> , |                                                         |

|         | Three Bears                           |                                                         |

| MQ      | _                                     | GeMSS, LUOV, MQDSS,                                     |

|         |                                       | Rainbow                                                 |

| Other   | _                                     | Picnic                                                  |

Table 1.2: Second-round and third-round NISTPQC candidates. Third round candidates are **bold**. Third round finalists are additionally **underlined**.

be useful for certain use cases. The code-based schemes in the NIST competition are mostly key-establishment schemes. They are characterized by large public keys and small ciphertexts. Hash-based cryptography can only be used to construct digital signatures, but not key establishment. It uses small public keys but results in large signatures. Isogeny-based cryptography only has a single candidate in the NIST competition: SIKE [JAC<sup>+</sup>17], which is a key-encapsulation mechanism. It has small public keys and ciphertexts but is significantly slower than other schemes. Lattice-based cryptography is the most prominent and arguably the promising family as it has reasonable ciphertext, signature, and public-key sizes, and also has a good performance. Last but not least, there are schemes based on the hardness of solving multivariate quadratic (MQ) equations. In the NIST competition, MQ schemes are mostly signature schemes. They are characterized by small signatures, but large public keys. There were also nine submissions that do not fit any of these five families. Sadly, none of the submissions comes without any disadvantages when compared to classical schemes like ECC: They either have much larger keys, larger ciphertexts, larger signatures, or are much slower.

In 2019, NIST published their first-round report [Nat19b] and announced the start of a second round with 26 candidate schemes advancing of which 17 are key-establishment schemes and nine are signature schemes. The second-round candidates are shown in Table 1.2. It is notable that all code-based signatures and all multivariate key-establishment schemes have been eliminated. Half of the candidates are based on lattices and still represent the most popular family of schemes. Note that only one scheme in the *other* family has survived the first round: Picnic [ZCD+17]. It is built using sym-

metric cryptography and zero-knowledge proofs. All other schemes have either been broken or been eliminated due to a lack of confidence in their security.

Another year later in mid-2020, NIST announced the third round [Nat20] with 15 schemes advancing. NIST distinguishes between seven finalists and eight alternate schemes. NIST states that finalists are likely ready for standardization at the end of the third round in case they are selected, while alternative schemes will require more research and further rounds of evaluation. It also states that due to similarities of the proposals it will standardize at most one of Kyber, NTRU, and Saber and will standardize at most one of Dilithium or Falcon, but not both.

NIST states that besides the security of the schemes and their key and message sizes, an important factor for selecting the future PQC standard is good performance [Nat19b]. Especially beyond the first round, performance is one of the most crucial factors unless significant cryptographic advances threaten the security of some schemes. It is essential that the selected schemes perform well on a wide range of platforms from smart cards and microcontrollers to high-end servers in a data center. To enable fair comparisons of implementations, NIST initially recommended that submission teams focus on 64-bit Intel processors. At the end of the first round, NIST announced that in addition to Intel processors, it would like the community to focus on Arm Cortex-M4 microcontrollers and Artix-7 FPGAs.<sup>2</sup>

In this thesis, I study how to implement selected NISTPQC candidates on the Arm Cortex-M4 to achieve the best performance. Compared to Intel processors, working on microcontrollers presents some challenges for PQC:

- Most importantly, memory is much more limited on microcontrollers, often not exceeding 100 kB. Many NISTPQC submissions require significant changes to the implementations to even be functional on such devices. Some schemes even have keys that are larger than the available memory which often hinders their use.

- The instruction sets of microcontrollers are much more limited than those of high-end Intel CPUs. While Intel implementations often exploit data-level parallelism using vector instructions, microcontrollers offer no or very limited ways to exploit data-level parallelism.

- Cryptographic hardware accelerators (e.g., for AES or SHA-2) are much less common in microcontrollers. While virtually all high-end processors now have specialized instructions for symmetric cryptography, these are usually non-existent on small devices. This results in

$<sup>^{1}</sup> https://csrc.nist.gov/projects/post-quantum-cryptography/post-quantum-cryptography-standardization/evaluation-process$

<sup>2</sup>https://groups.google.com/a/list.nist.gov/g/pqc-forum/c/cJxMq0\_90gU/m/ qbGEs3TXGwAJ

a big slow-down for PQC schemes relying on symmetric cryptography as a building block which is the case for most schemes.

- Microcontrollers run at a much lower frequency than high-end CPUs, which results in some schemes taking seconds or even minutes. For many use cases, this can be prohibitively slow.

- Energy consumption is a much larger concern for microcontrollers as they are often embedded into battery-powered systems.

- Library support is much more limited for microcontrollers. Even if libraries are available, they are often not heavily optimized for the target architecture. This usually requires replacing all libraries with custom optimized code.

Overarching of the work presented in this thesis is the pqm4 [KPR<sup>+</sup>] project which was started in early 2018 by Rijneveld, Stoffelen, Schwabe, and myself. pqm4 is a unified testing and benchmarking framework for NISTPQC schemes on the Arm Cortex-M4. Initially, the goal was to make as many schemes as possible work while making sure that the implementations are compatible with the reference implementations running on a high-end CPU. The unified benchmarking framework was used by many optimization papers to obtain fair performance metrics including speed, memory consumption, and code size. To ensure consistency and accessibility, pqm4 collects all optimized (open-source) implementations and posts the performance benchmarks online.

Research Data Management. This thesis research has been carried out under the research data management policy of the Institute for Computing and Information Science of Radboud University, The Netherlands. The research datasets produced during this PhD research packaged into a single archive are available at https://doi.org/10.5281/zenodo.5555735. For more details, see Appendix A.

## 1.1 Contributions

The content in the main body of this thesis is the result of collaboration and publication with multiple co-authors. As usual in the field of cryptography, all publications list authors in alphabetical order as it is usually not possible to identify one main author. Nonetheless, my contributions to these publications vary and the following section outline which parts are my contributions.

### Part I: Multiplication for NTT-friendly Rings

In the first content part of this thesis, we study implementations of postquantum KEMs and signature schemes which have been specifically designed to benefit from using number-theoretic transforms (NTTs) for polynomial arithmetic. The part is based on two publications published at Africacrypt 2019 and TCHES 2021.

Leon Botros, Matthias J. Kannwischer, and Peter Schwabe. Memory-efficient high-speed implementation of Kyber on Cortex-M4. In *Progress in Cryptology – Africacrypt 2019*, LNCS, pages 209–228. Springer, 2019. https://eprint.iacr.org/2019/489

This work, contained in Chapter 3, studies Cortex-M4 implementations of the Kyber KEM both with and without the changes that have been introduced in the second round of the NIST competition. The paper discusses implementations optimized for speed and for stack consumption. I wrote all the assembly code involved in the polynomial arithmetic. The stack optimized implementations are based on a Cortex-M0 implementation by Leon Botros, that I ported to the M4 implementation together with him. The writing of the paper was a joint effort of all authors.

Denisa O. C. Greconici, Matthias J. Kannwischer, and Daan Sprenkels. Compact Dilithium implementations on Cortex-M3 and Cortex-M4. *IACR Transactions on Cryptographic Hardware and Embedded Systems*, 2021(1):1–24, 2020. https://eprint.iacr.org/2020/1278

The second publication is presented in Chapter 4. It presents new speed-records for the signature scheme Dilithium on the Cortex-M4, and additionally presents the first implementations for Dilithium, Kyber, and NewHope on the Cortex-M3. We provide several time-memory trade-offs for the signature generation of Dilithium. The Cortex-M3 implementation of the Dilithium NTT is the core contribution to which all authors contributed equally. Additionally, I wrote the faster Cortex-M4 NTT as well as the Cortex-M3 implementations of Kyber and NewHope. Paper writing was distributed equally between authors.

## Part II: Multiplication for NTT-unfriendly Rings

While some schemes are specifically designed to benefit from NTT multiplication, other lattice-based schemes are built using different polynomial rings which allow various ways of implementing polynomial arithmetic. The most prominent schemes in that realm are Saber and NTRU which to date are still candidates for the NISTPQC standardization. Implementations of those were studied in two papers published at ACNS 2019 and TCHES 2021.

Matthias J. Kannwischer, Joost Rijneveld, and Peter Schwabe. Faster multiplication in  $\mathbb{Z}_{2^m}[x]$  on Cortex-M4 to speed up NIST PQC candidates. In *Applied Cryptography and Network Security – ACNS 2019*, LNCS, pages 281–301. Springer, 2019. https://eprint.iacr.org/2018/1018

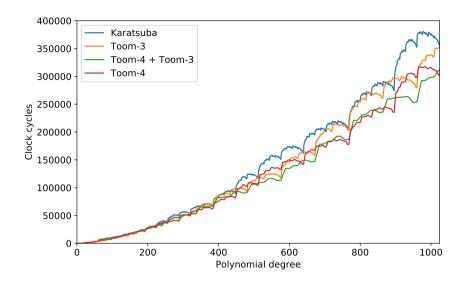

Chapter 5 covers the earlier work which describes how five first-round candidates (including Saber and NTRU) relying on polynomial multiplication in  $\mathbb{Z}_{2^m}[x]$  can be efficiently implemented on the Cortex-M4 using Karatsuba multiplication and Toom–Cook multiplication. As the polynomial rings used in these five schemes vary significantly, the main contribution of this work is a code generator supporting arbitrary polynomial degrees and allowing a number of different combination of multiplication methods. The code generation was written in close collaboration with Joost Rijneveld with the help of the blackboard in our beautiful corner office in Nijmegen. The paper was written by all three authors. We have received the ACNS 2019 best student paper award for this paper.

Chi-Ming Marvin Chung, Vincent Hwang, Matthias J. Kannwischer, Gregor Seiler, Cheng-Jhih Shih, and Bo-Yin Yang. NTT multiplication for NTT-unfriendly rings – new speed records for Saber and NTRU on Cortex-M4 and AVX2. *IACR Transactions on Cryptographic Hardware and Embedded Systems*, 2021(2):159–188, 2021. https://eprint.iacr.org/2020/1397

The second publication presents how polynomial multiplication can be implemented even more efficiently by using the NTT. The details are covered in Chapter 6. We showcase the superiority of NTT implementations compared to Toom—Cook and Karatsuba multiplication for the three KEMs NTRU, Saber, and LAC and target the Cortex-M4 and AVX2. While the former two are currently still under consideration by NIST, the later scheme has been chosen as a winner of the Chinese Association for Cryptologic Research (CACR) post-quantum competition. The Cortex-M4 code is a result of a summer internship by Chi-Ming Marvin Chung, Vincent Hwang, and Cheng-Jhih Shih at Academia Sinica, Taiwan that was supervised by Bo-Yin Yang and me. Vincent Hwang and I got these implementations into shape for publication. The AVX2 implementations are by Gregor Seiler. The paper was written by Vincent Hwang, Gregor Seiler, Bo-Yin Yang, and me. We have received the TCHES 2021 best artifact award for the code submitted alongside this paper.

## Other publications

I have chosen not to include various other publications in this thesis, as it allows me to spend more words on connecting the selected work and elaborate

on the common preliminaries in greater depth. The peer-reviewed academic publications not appearing in this thesis in reverse chronological order are:

- Hanno Becker, Vincent Hwang, Matthias J. Kannwischer, Bo-Yin Yang, and Shang-Yi Yang. Neon NTT: Faster Dilithium, Kyber, and Saber on Cortex-A72 and Apple M1. *IACR Transactions on Cryptographic Hardware and Embedded Systems*, 2022(1):221–244, 2021. https://eprint.iacr.org/2021/986

- Amin Abdulrahman, Jiun-Peng Chen, Yu-Jia Chen, Vincent Hwang, Matthias J. Kannwischer, and Bo-Yin Yang. Multi-moduli NTTs for Saber on Cortex-M3 and Cortex-M4. *IACR Transactions on Cryptographic Hardware and Embedded Systems*, 2022(1):127–151, 2021. https://eprint.iacr.org/2021/995

- Ruben Gonzalez, Andreas Hülsing, Matthias J. Kannwischer, Juliane Krämer, Tanja Lange, Marc Stöttinger, Elisabeth Waitz, Thom Wiggers, and Bo-Yin Yang. Verifying post-quantum signatures in 8 kB of RAM. In *Post-Quantum Cryptography - PQCrypto 2021*, LNCS, pages 215–233. Springer, 2021. https://eprint.iacr.org/2021/662

- Tung Chou, Matthias J. Kannwischer, and Bo-Yin Yang. Rainbow on Cortex-M4. *IACR Transactions on Cryptographic Hardware and Embedded Systems*, 2021(4):650–675, 2021. https://eprint.iacr.org/2021/532

- Fabio Campos, Matthias J. Kannwischer, Michael Meyer, Hiroshi Onuki, and Marc Stöttinger. Trouble at the CSIDH: Protecting CSIDH with dummy-operations against fault injection attacks. In *Workshop on Fault Detection and Tolerance in Cryptography*, pages 57–65, 2020. https://eprint.iacr.org/2020/1005

- Matthias J. Kannwischer, Peter Pessl, and Robert Primas. Single-trace attacks on Keccak. IACR Transactions on Cryptographic Hardware and Embedded Systems, 2020(3):243-268, 2021. https://eprint.iacr. org/2020/371

- Matthias J. Kannwischer, Aymeric Genêt, Denis Butin, Juliane Krämer, and Johannes Buchmann. Differential power analysis of XMSS and SPHINCS. In Constructive Side-Channel Analysis and Secure Design COSADE 2018, pages 168-188. Springer, 2018. https://eprint.iacr.org/2018/673

Beyond these formally published publications, the following papers have been accepted to conferences and workshops without formal proceedings:

• Matthias J. Kannwischer, Joost Rijneveld, Peter Schwabe, and Ko Stoffelen. pqm4: Testing and benchmarking NISTPQC on ARM Cortex-M4. In Second NIST PQC Standardization Conference, 2019. https://eprint.iacr.org/2019/844

Aymeric Genêt, Matthias J. Kannwischer, Hervé Pelletier, and Andrew McLauchlan. Practical fault injection attacks on SPHINCS. In Kangacrypt, 2018. https://eprint.iacr.org/2018/674

In addition to these papers, I am involved in the NISTPQC signature finalist Rainbow:

• Jintai Ding, Ming-Shing Chen, Matthias Kannwischer, Jacques Patarin, Albrecht Petzoldt, Dieter Schmidt, and Bo-Yin Yang. Rainbow: Algorithm specification and supporting documentation. Submission to the NIST Post-Quantum Cryptography Standardization Project [NIS16], 2019. https://www.pqcrainbow.org/

## Chapter 2

## **Preliminaries**

This chapter presents the preliminaries that are common among the following chapters of this thesis. Section 2.1 introduces the basic terminology of key-establishment and digital signature schemes. Section 2.2 presents polynomial-multiplication techniques with a focus on fast software implementations. Section 2.3 introduces algorithms for fast modular arithmetic, which is used as a building block of polynomial multiplication. Lastly, Section 2.4 presents the primary optimization platforms throughout this thesis: the Arm Cortex-M4 and Arm Cortex-M3.

## 2.1 Cryptographic Schemes

The NISTPQC competition seeks post-quantum replacements for the NIST standards for key-establishment schemes and digital signature schemes. The following sections introduce the terminology that is commonly used when describing those schemes. It discusses the security properties that are generally desired for such schemes. While these definitions are not limited to post-quantum cryptography, a scheme is called post-quantum in case the security properties still hold in case the adversary has a large-scale quantum computer.

## 2.1.1 Key-Establishment Schemes

The objective of key establishment is for two (or more) parties to agree on a shared secret key. Cryptographically this can be achieved in multiple different ways including either a PKE, a KEM, or a non-interactive key exchange (NIKE). Up until recently, post-quantum schemes were limited to either PKE or KEM. In 2018, after the deadline of the NIST project has passed, also post-quantum NIKE based on isogenies has been proposed [CLM<sup>+</sup>18].

However, as this came long after NIST called for proposals, NIST only allowed PKE and KEM submissions. As shown in the following, it is easy to construct a KEM from a PKE and vice versa.

A PKE scheme consists of three algorithms: KeyGen, Encrypt, and Decrypt:

KeyGen() takes no inputs and outputs a key pair consisting of a public key pk and a secret key sk.

Encrypt(pk, m) takes as inputs a public key pk and a message m, which is usually a bitstring. It outputs the encrypted message as ciphertext c.

Decrypt(sk, c) takes as inputs a secret key sk and a ciphertext c. It outputs the decrypted message m'.

A PKE scheme is correct if Decrypt(sk, Encrypt(pk, m)) = m for any key pair (pk, sk) produced by KeyGen() and any message m. It is called a deterministic PKE (DPKE) if Encrypt outputs the same ciphertext if called with the same inputs multiple times. Any non-deterministic PKE can be turned into a DPKE by slightly changing the API and making the randomness an explicit argument, e.g., by adding an argument seed that is used to derive all randomness pseudo-randomly.

A key-encapsulation mechanism (KEM) consists of three algorithms: KeyGen, Encaps, and Decaps:

KeyGen() takes no inputs and outputs a key pair consisting of a public key pk and a secret key sk.

Encaps(pk) takes as input a public key pk and returns a ciphertext c and a session key ss.

Decaps(sk, c) takes as input a secret key sk and a ciphertext c. It outputs

a session key ss'.

A KEM is correct if given  $c, ss \leftarrow Encaps(pk)$ , Decaps(sk, c) = ss for any key pair (pk, sk) produced by KeyGen(). To formalize the security of cryptographic schemes one usually describes the capabilities of the most powerful attack that a cryptographic scheme can resist. The most common security notion of PKE schemes and KEMs is indistinguishability under chosen-plaintext attacks (IND-CPA; CPA for short) and indistinguishability under chosen-ciphertext attacks (IND-CCA; CCA for short). Informally, these notations can be explained as follows. Indistinguishability refers to the inability of an attacker to reliably distinguish which of two ciphertexts corresponds to a given message. In the CPA setting, the adversary can encrypt as many messages as needed to obtain information from the ciphertexts that help to distinguish the given setting. This implies that a DPKE can never be CPA secure as the adversary can simply encrypt the given message. In

the CCA setting, the adversary is more powerful: He can actively choose ciphertexts (different from the target ciphertexts) and ask a decryption oracle to decrypt those. The information obtained from those queries must not help him to distinguish the ciphertexts. CPA attacks are also called passive attacks, while CCA attacks are called active attacks referring to the adversary actively tampering with some ciphertexts to obtain information about the secret key.

In practice, in most settings, the desired security notion is CCA security as it can often not be guaranteed that the adversary is unable to mount active attacks. For example, consider a public web server responding to requests. An adversary can send crafted ciphertexts to the web server that it will decrypt; the behavior of the web server often can be used to obtain some information about the secret key involved. Hence, it is usually only acceptable to use a CPA-secure scheme if each public key is only used once.

Luckily, there exist constructions that transform CPA-secure schemes into CCA-secure schemes. The most common one is the Fujisaki—Okamoto (FO) [FO99] transform which allows transforming a CPA-secure DPKE into a CCA-secure KEM. This approach is used by a large number of NISTPQC schemes including most of the ones covered in this thesis. Informally, the FO transform allows the decrypting party to verify that the ciphertext was honestly generated or if it was crafted. In case a dishonest ciphertext is detected, a random key is returned such that no information about the secret key is revealed. For a more formal description of the construction refer to [HHK17].

## 2.1.2 Digital Signature Schemes

A digital signature scheme consists of three algorithms: KeyGen, Sign, and Open:

- KeyGen() takes no inputs and outputs a key pair consisting of a public key pk and a secret key sk.

- Sign(sk, m) takes as inputs a secret key sk and a message m which is usually a bitstring of arbitrary length. It outputs a signed message sm commonly consisting of the concatenation of the message itself and a signature.

- Open(pk, sm) takes as inputs a public key pk and a signed message sm. If the signature is valid under pk, it returns the message m. Otherwise, it returns an error.

A digital signature scheme is called correct if Open(pk, Sign(sk, m)) = m for any (pk, sk) produced by KeyGen() and any message m. There is an alternative definition of signature schemes where Sign returns a signature rather than a signed message, which is then verified using an algorithm

Verify. In that case, it is left to the user of the cryptographic scheme to decide what to do in case a signature is invalid. This can have catastrophic consequences as users (e.g., implementers using a cryptographic library) will often ignore such failure and proceed as usual. In the vast majority of cases, the sensible action to do is to discard the message and trigger some kind of error handling as the message cannot be trusted. This is the behavior enforced by the Sign/Open definition of signature schemes. NIST is following the Sign/Open definitions and requires the submitted software to adhere to the APIs reflecting them.

For a digital signature scheme to be secure, we require that it is impossible to produce a valid signed message sm without the knowledge of the secret key sk. The most common security notion for signature schemes is existential unforgeability under chosen message attacks (EU-CMA). Informally, it implies that an adversary is incapable to produce a signature for any message (existential forgery) even if he is allowed to obtain signatures for other messages, i.e., has access to a signing oracle.

# 2.2 Polynomial Multiplication for Computer Scientists

For thousands of years, humankind has studied how to efficiently multiply, either in anticipation of intriguing applications like cryptography or for its mere mathematical beauty. Hence, we can now choose from a plethora of multiplication methods that may or may not be useful for the problem at hand. Polynomial multiplication is a core building block for cryptography of all kinds. In particular, the vast majority of post-quantum schemes use polynomial multiplication. A closely related task is the multiplication of large integers which is used in yet another large number of cryptographic schemes.

Even more, multiplication methods are constantly adapted and optimized for a certain instance, such that any given implementation of polynomial multiplication contains dozens of tricks that have been discovered in decades or even centuries of research. This makes it incredibly hard to understand a given implementation without reading a huge number of papers. This is amplified by the fact that most tricks are simply part of all modern implementations, but rarely fully explained or attributed to the corresponding publications.

To date, I am not aware of any good comprehensive introduction to all polynomial multiplication methods used in state-of-the-art implementations of post-quantum cryptographic schemes. The renowned work by Bernstein [Ber01] is an excellent survey of numerous tricks and concisely presents them for a reader with experience in the underlying mathematical concepts. However, coming from a computer science background and lacking the nec-

essary mathematical background, it appears to be hardly decipherable. As I struggled for many years to conceive the tricks and I have seen many students struggle with it in the same way, I have decided to try to bridge this gap and write an introduction to polynomial multiplication for computer scientists.

In the following sections, I present every single way of multiplying polynomials that I have encountered in actual implementations of post-quantum cryptographic schemes over the years. Alongside the descriptions in this thesis, each section comes with sample implementations in Python and C. I aimed for this chapter to be brief, self-contained, and easy to follow. In parts, I skip over a lot background and formal definitions and instead provide examples that I hope provide a good intuition and serve as a starting point. For a more formal treatment, I recommend reading [vzGG13], [Nus82], and of course [Ber01].

The code is available at https://github.com/mkannwischer/polymul and can be freely used under a CC0 copyright waiver. All source code related to this thesis is also available in a single archive. See Appendix A.

Notation. Let  $\mathbb{Z}$  be the ring of integers, and  $\mathbb{Z}_q$  be the integer ring containing  $\{0,...,q-1\}$  with q being a positive integer and arithmetic being performed modulo q. We write  $\mathbb{Z}[x]$  to denote the polynomial ring in the variable x with integer coefficients, and  $\mathbb{Z}_q[x]$  to denote the polynomial ring with coefficients in  $\mathbb{Z}_q$ . Given a polynomial a in some polynomial ring, we write  $a_i$  to denote the coefficient corresponding to  $x^i$ , i.e,  $a = \sum_{i=0}^{n-1} a_i x^i$ . As these polynomial rings have an infinite number of elements, they are not particularly useful for cryptography. Hence, one uses a finite polynomial ring instead by computing modulo a certain polynomial f(x) with degree n, such that polynomials remain at degree at most n-1, i.e., n coefficients. We write  $\mathbb{Z}_q[x]/(f(x))$  to denote the ring with all operations modulo f(x) and q. Sometimes we require to split a polynomial a into multiple parts by setting  $y = x^k$  for some k < n. To denote the part i, we write  $a^{(i)}$ , such that  $a = \sum_{i=0}^{\lceil n/k \rceil} a^{(i)} y^i$ .

**Example 1:** Consider the polynomial ring  $\mathbb{Z}_2[x]/(x^2+1)$ . This polynomial ring has four elements:  $\{0,1,x,x+1\}$ . We can now multiply two polynomials, e.g.,  $x \cdot (x+1) = x^2 + x \equiv x+1 \pmod{q,x^2+1}$  as  $x^2 \equiv -1 \pmod{q,x^2+1}$ .

For cryptographic purposes, one uses polynomial rings with many more elements. In the following we are mostly considering rings that are used in cryptographic schemes based upon structured lattices, but all of the algorithms find application far beyond. A common choice for q is either a power of two or a prime, commonly below 32 or 16 bits, such that one or two coefficients fit neatly into a processor word on all popular platforms. A common choice for n is between 256 and 1024. For some polynomial multiplication

algorithms, n is ideally a power of two as well, but that is not always the case in cryptographic schemes. A very common choice for f(x) is  $x^n + 1$  or  $x^n - 1$  as the reduction is simple to implement and can often be done on the fly.

**Application:** Kyber [ABD<sup>+</sup>17] uses the ring  $\mathbb{Z}_{3329}[x]/(x^{256} + 1)$ , Saber [DKRV17] uses  $\mathbb{Z}_{8192}[x]/(x^{256} + 1)$ , NTRU [ZCH<sup>+</sup>19] uses (among others)  $\mathbb{Z}_{8192}[x]/(x^{701} - 1)$ , and Dilithium [LDK<sup>+</sup>17] uses  $\mathbb{Z}_{8380417}[x]/(x^{256} + 1)$ .

Coefficient Multiplication. Every polynomial-multiplication algorithm requires multiplying elements in  $\mathbb{Z}_q$ . Since q is chosen such that coefficients fit into registers, multiplication can in most cases use the available multiplication instructions which multiply mod  $2^k$  with  $k \in 16, 32, 64$ . If q is a power of two, one can simply use the instruction  $2^k > q$  and obtain the standard representative (0, ..., q-1) using a logical AND with q-1. For intermediate values, the standard representative is usually not required, and one can omit the reductions. However, if q is not a power of two, the multiplication needs to be performed mod  $2^k > q^2$  and needs to be followed by an explicit reduction modulo q to bring coefficients back to a single word. Furthermore, additions and subtractions of coefficients cause them to grow and one needs to be careful to reduce them before they overflow the word size. For reductions after multiplications, one commonly uses Montgomery reductions [Mon85], while for reductions after additions, one can use Montgomery reductions, Barrett reductions [Bar86], or specialized reductions for special primes, e.g., Solinas primes [Sol99]. For describing the polynomialmultiplication algorithms, we assume that modular multiplications in  $\mathbb{Z}_q$ can be performed efficiently and cover the concrete algorithms separately in Section 2.3.

**Convolution.** In literature about polynomial multiplication one often also reads about convolution, positively wrapped (or cyclic) convolution, and negatively wrapped (or negacyclic) convolution. In general, convolution (written as \*) of two functions f(x) and g(x) is defined as [Nus82, Sec 2.2.4]

$$[f * g](x) = \int f(\tau)g(x - \tau) d\tau.$$

However, if f and g are polynomials in  $\mathbb{Z}[x]$  (or  $\mathbb{Z}_q[x]$ ), the convolution of f and g is equivalent to polynomial multiplication. Similarly, cyclic convolution is equivalent to multiplication in  $\mathbb{Z}[x]/(x^n-1)$  (or  $\mathbb{Z}_q[x]/(x^n-1)$ ), and negacyclic convolution is equivalent to multiplication in  $\mathbb{Z}[x]/(x^n+1)$  (or  $\mathbb{Z}_q[x]/(x^n+1)$ ). These terms are often used interchangeably.

Figure 2.1: Schoolbook multiplication of polynomials  $a = a_2x^2 + a_1x + a_0$  and  $b = b_2x^2 + b_1x + b_0$

## 2.2.1 Schoolbook Multiplication

Before diving into the different algorithms available for polynomial multiplication, it makes sense to revisit the problem at hand and its straightforward solution: Given two n-coefficient polynomials a, b in some polynomial ring, we want to compute the product  $a \cdot b$ . In case the polynomial ring is  $\mathbb{Z}[x]$  or  $\mathbb{Z}_a[x]$ , the multiplication is defined as

$$a \cdot b = \sum_{i=0}^{n-1} \sum_{j=0}^{n-1} a_i \cdot b_j \cdot x^{i+j}.$$

In case the polynomial ring is  $\mathbb{Z}[x]/(x^n-1)$ , the multiplication becomes

$$a \cdot b \equiv \sum_{i=0}^{n-1} \sum_{j=0}^{n-i-1} a_i \cdot b_j \cdot x^{i+j} + \sum_{j=1}^{n-1} \sum_{i=n-j}^{n-1} a_i \cdot b_j \cdot x^{i+j-n} \pmod{x^n-1}.$$

Similarly, for  $\mathbb{Z}[x]/(x^n+1)$  the multiplication is defined as

$$a \cdot b \equiv \sum_{i=0}^{n-1} \sum_{j=0}^{n-i-1} a_i \cdot b_j \cdot x^{i+j} - \sum_{j=1}^{n-1} \sum_{i=n-j}^{n-1} a_i \cdot b_j \cdot x^{i+j-n} \pmod{x^n+1}.$$

As we usually work with polynomial rings over  $\mathbb{Z}_q$  rather than over  $\mathbb{Z}$ , the intermediate addition and multiplication of coefficients can be performed modulo q.

**Example 2:** Let

$$a = x^2 + 2x + 3$$

,  $b = x^2 + x$ .

In  $\mathbb{Z}[x]$ , the product is  $x^4 + 3x^3 + 5x^2 + 3x$ .

In  $\mathbb{Z}[x]/(x^3 - 1)$ , the product is  $(5x^2 + 3x) + (x + 3) = 5x^2 + 4x + 3$ .

In  $\mathbb{Z}[x]/(x^3 + 1)$ , the product is  $(5x^2 + 3x) - (x + 3) = 5x^2 + 2x - 3$ .

These three multiplications are illustrated for 3-coefficient polynomials in Figure 2.1. When implementing schoolbook multiplication, there exist two

different approaches: Either one fixes a coefficient  $a_i$  and iterates through all coefficients of b. This corresponds to computing one row in Figure 2.1 and is called operand scanning. Alternatively, one uses product scanning, where one column in Figure 2.1 is computed at a time.

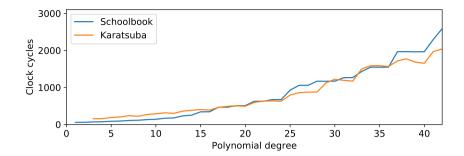

Note that the number of multiplications of coefficients required for all these algorithms is  $n^2$ , while the number of additions is  $(n-1)^2$ . For small n it is often the case that schoolbook multiplication is actually the fastest approach available as most other approaches work by breaking down a larger multiplication into multiple smaller ones which incur some overhead that may outweigh the gain. The actual cut-off point for each method not only depends on the polynomial ring, but also on the available multipliers and adders on the target platform and their respective performance characteristics. Hence, it is important to understand the optimal approach to implement schoolbook multiplication.

**Application:** Schoolbook multiplication of small polynomials is often used as a building block in other multiplications methods. Chapter 5 describes extensive optimization on the Arm Cortex-M4 of schoolbook multiplications for polynomials with eight to 16 coefficients applicable, for example, to Saber [DKRV17] and NTRU [ZCH<sup>+</sup>19].

## 2.2.2 Karatsuba Multiplication

Karatsuba's multiplication method [KO63] allows breaking down a large polynomial multiplication (n-coefficient multiplicands) into three smaller polynomial multiplications with n/2-coefficient multiplicands. The following example illustrates Karatsuba's idea.

**Example 3:** Consider the most straightforward example with 2-coefficient inputs  $a = a_1x + a_0$  and  $b = b_1x + b_0$ . The schoolbook method from the previous section would compute the product  $a \cdot b$  as

$$a \cdot b = (a_1x + a_0)(b_1x + b_0) = a_1b_1x^2 + (a_0b_1 + a_1b_0)x + a_0b_0.$$

This requires four coefficient multiplications and one coefficient addition. The Karatsuba algorithm exploits the fact that

$$(a_0b_1 + a_1b_0) = (a_0 + a_1)(b_0 + b_1) - a_1b_1 - a_0b_0.$$

It hence computes the product as

$$a \cdot b = (a_1x + a_0)(b_1x + b_0) = a_1b_1x^2 + ((a_0 + a_1)(b_0 + b_1) - a_1b_1 - a_0b_0)x + a_0b_0.$$

This now requires five coefficient products. However,  $a_0b_0$  and  $a_1b_1$  are used twice, consequently, we only need to compute three coefficient multiplications. Despite the savings in multiplications, we now also require more additions. In total, four additions are needed.

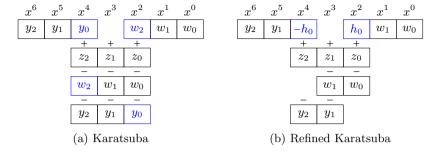

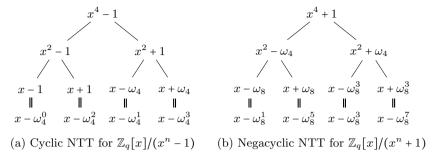

This approach can be easily generalized to arbitrary-degree polynomials. Consider  $a = \sum_{i=0}^{n-1} a_i x^i$ ,  $b = \sum_{i=0}^{n-1} b_i x^i$ . We now set  $t = x^{\left\lfloor \frac{n}{2} \right\rfloor}$ , and rewrite  $a = a^{(1)}t + a^{(0)}$ ,  $b = b^{(1)}t + b^{(0)}$  where  $a^{(0)}$  and  $b^{(0)}$  are  $\left\lfloor \frac{n}{2} \right\rfloor$ -coefficient polynomials consisting of the lower half of the coefficients of a and b. Conversely,  $a^{(1)}$  and  $b^{(1)}$  are  $\left\lceil \frac{n}{2} \right\rceil$ -coefficient polynomials consisting of the upper half of the coefficients of a and b. We can then use Karatsuba, to compute  $a \cdot b$  using  $a^{(0)} \cdot b^{(0)}$ ,  $a^{(1)} \cdot b^{(1)}$ , and  $a^{(0)} \cdot b^{(1)} \cdot b^{(1)} \cdot b^{(1)}$ . Note that the smaller multiplications are now  $\left\lfloor \frac{n}{2} \right\rfloor$ -coefficient polynomial multiplications. We illustrate the Karatsuba trick for n = 4 in Figure 2.2a.

Recursive Karatsuba. For large-degree inputs, this approach can be applied recursively. We can break down an n-coefficient multiplication into three n/2-coefficient multiplications each of which gets broken down into three n/4-coefficient multiplications. This is called applying multiple layers of Karatsuba. Each additional layer introduces more additions while saving some multiplications. It is likely that it is not optimal to do this all the way down to 1-coefficient polynomials at which polynomial multiplication becomes trivial, but rather one wants to stop earlier and perform a schoolbook multiplication of small-degree polynomials.

Figure 2.2: Karatsuba multiplication and refined Karatsuba multiplication for polynomials  $a = a_0 + a_1x + a_2x^2 + a_3x^3$ ,  $b = b_0 + b_1x + b_2x^2 + b_3x^3$ . Let  $w = (a_0 + a_1x)(b_0 + b_1x)$ ,  $y = (a_2 + a_3x)(b_2 + b_3x)$ ,  $z = ((a_0 + a_2) + (a_1 + a_3)x)((b_0 + b_2) + (b_1 + b_3)x)$ . For refined Karatsuba, let  $b = w_2 - y_0$ .

**Example 4:** A common approach for multiplying 256-coefficient polynomials is to use four layers of Karatsuba and then switch to schoolbook multiplication. The schoolbook multiplications handle polynomials with 256/16 = 16 coefficients and we need a total of  $3^4 = 81$  of them.

**Refined Karatsuba.** Looking at Figure 2.2a, one can see that the term  $x_2 - y_0$  appears twice in our product. Once for coefficient  $c^{(2)}$ , and once for coefficient  $c^{(4)}$  (as  $y_0 - x_2$ ). We can exploit this fact and simply compute the subtraction once as  $h = x_2 - y_0$ . The result is what is referred to as refined Karatsuba [Ber01] and is shown in Figure 2.2b. Assuming inputs of n coefficients, this trick can save  $(n/2) \cdot 2 - 1 = n - 1$  subtractions. Note, however, that this will only work if the negation of n can be computed for free. This can be achieved by computing  $x_2 - h$  rather than  $x_2 - h$  rather than  $x_3 - h$  rather than  $x_4 - h$  rather than

**Application:** Chapter 5 describes how to use recursive refined Karatsuba to implement efficient multiplications of polynomials of degree 16 to about 256 on the Arm Cortex-M4. Below degree 16 schoolbook multiplication is superior, above 256 Toom-Cook outperforms Karatsuba.

## 2.2.3 Toom-Cook Multiplication

The idea of splitting up input polynomials into smaller polynomials as done by Karatsuba's multiplication algorithm can be generalized to split into a larger number of polynomials. One such generalization is Toom–Cook multiplication [Too63, Coo66]. N-way Toom–Cook (or Toom-N for short) is splitting polynomials with n coefficients into N parts of n/N coefficients each. The underlying smaller polynomial multiplications will then process polynomials of n/N coefficients.

For example, Toom-3 splits inputs into three parts of n/3 coefficients. This is done in the following way: We substitute  $y=x^{n/3}$  and write the polynomial a as  $y^2a^{(2)}+ya^{(1)}+a^{(0)}$  and proceed similarly for the input b. The goal is now to compute the product

$$c = a \cdot b = y^4 c^{(4)} + y^3 c^{(3)} + y^2 c^{(2)} + y c^{(1)} + c^{(0)}$$

.

Toom–Cook does so by evaluating the polynomial a and b at certain values of y, then multiplying the smaller n/N polynomials, such that c can be recovered from the smaller products using interpolation. For Toom-3, this requires five values for y. A common choice is  $y = \{0, 1, -1, -2, \infty\}$  with  $a(\infty) = a^{(2)}$  Evaluating a and b yields

$$\begin{bmatrix} a(0) \\ a(1) \\ a(-1) \\ a(-2) \\ a(\infty) \end{bmatrix} = \begin{bmatrix} 1 & 0 & 0 \\ 1 & 1 & 1 \\ 1 & -1 & 1 \\ 1 & -2 & 4 \\ 0 & 0 & 1 \end{bmatrix} \begin{bmatrix} a^{(0)} \\ a^{(1)} \\ a^{(2)} \end{bmatrix} \quad \text{and} \quad \begin{bmatrix} b(0) \\ b(1) \\ b(-1) \\ b(-2) \\ b(\infty) \end{bmatrix} = \begin{bmatrix} 1 & 0 & 0 \\ 1 & 1 & 1 \\ 1 & -1 & 1 \\ 1 & -2 & 4 \\ 0 & 0 & 1 \end{bmatrix} \begin{bmatrix} b^{(0)} \\ b^{(1)} \\ b^{(2)} \end{bmatrix}.$$

By pointwise multiplication, we obtain five points of  $c = a \cdot b$  which is sufficient to recover the polynomial  $y^4c^{(4)} + y^3c^{(3)} + y^2c^{(2)} + yc^{(1)} + c^{(0)}$ .

Given that

$$\begin{bmatrix} a(0) \cdot b(0) \\ a(1) \cdot b(1) \\ a(-1) \cdot b(-1) \\ a(-2) \cdot b(-2) \\ a(\infty) \cdot b(\infty) \end{bmatrix} = \begin{bmatrix} c(0) \\ c(1) \\ c(-1) \\ c(-2) \\ c(\infty) \end{bmatrix} = \begin{bmatrix} 1 & 0 & 0 & 0 & 0 \\ 1 & 1 & 1 & 1 & 1 \\ 1 & -1 & 1 & -1 & 1 \\ 1 & -2 & 4 & -8 & 16 \\ 0 & 0 & 0 & 0 & 1 \end{bmatrix} \begin{bmatrix} c^{(0)} \\ c^{(1)} \\ c^{(2)} \\ c^{(3)} \\ c^{(4)} \end{bmatrix}$$

we can obtain  $c^{(0)}, c^{(1)}, c^{(2)}, c^{(3)}$ , and  $c^{(4)}$  by inverting the matrix as

$$\begin{bmatrix} c^{(0)} \\ c^{(1)} \\ c^{(2)} \\ c^{(3)} \\ c^{(4)} \end{bmatrix} = \begin{bmatrix} 1 & 0 & 0 & 0 & 0 \\ 1/2 & 1/3 & -1 & 1/6 & -2 \\ -1 & 1/2 & 1/2 & 0 & -1 \\ -1/2 & 1/6 & 1/2 & -1/6 & 2 \\ 0 & 0 & 0 & 0 & 1 \end{bmatrix} \begin{bmatrix} c(0) \\ c(1) \\ c(-1) \\ c(-2) \\ c(\infty) \end{bmatrix}.$$

This immediately reveals a disadvantage of Toom multiplication. In the case of Toom-3, one needs to be able to divide by 3 and 2. As we are commonly working in a finite ring  $\mathbb{Z}_q$ , this presents a challenge. In general, there are two ways this can be achieved: If working in  $\mathbb{Z}_q$  with q co-prime to 2 and 3, one can simply multiply by the inverses of 2 and 3. However, if q is not co-prime to either 2 or 3, this is no longer possible. To counter this issue, we instead need to do all computations modulo a larger q', such that we can be sure that whenever we need to do divisions, the remainder will always

#### Algorithm 1 Toom-3 evaluation and interpolation sequence

```

Input: a = a^{(0)} + a^{(1)}y + a^{(2)}y^2, b = b^{(0)} + b^{(1)}y + b^{(2)}y^2

Output: c = a \cdot b = c^{(0)} + c^{(1)}y + c^{(2)}y^2 + c^{(3)}y^3 + c^{(4)}y^4

1: a(0) \leftarrow a^{(0)} \quad b(0) \leftarrow b^{(0)} \quad \triangleright \text{ Evaluate } a \text{ and } b \text{ at } y_i = \{0, 1, -1, -2, \infty\}

2: t \leftarrow a^{(0)} + a^{(2)} \quad a(1) \leftarrow t + a^{(1)} \quad a(-1) \leftarrow t - a^{(1)}

3: t \leftarrow b^{(0)} + b^{(2)} \quad b(1) \leftarrow t + b^{(1)} \quad b(-1) \leftarrow t - b^{(1)}

4: a(-2) \leftarrow a^{(0)} - 2a^{(1)} + 4a^{(2)} \quad b(-2) \leftarrow b^{(0)} - 2b^{(1)} + 4b^{(2)}

5: a(\infty) \leftarrow a^{(2)} \quad b(\infty) \leftarrow b^{(2)}

6: ... \Rightarrow \text{Perform small mults to obtain } c(0), c(\infty), c(1), c(-1), c(-2)

7: c^{(0)} \leftarrow c(0) \quad c^{(4)} \leftarrow c(\infty) \Rightarrow \text{Interpolate } c

8: t_1 \leftarrow (c(-2) - c(1))/3 \Rightarrow -c^{(1)} + c^{(2)} - 3c^{(3)} + 5c^{(4)}

9: t_2 \leftarrow (c(1) - c(-1))/2 \Rightarrow c^{(1)} + c^{(3)}

10: t_3 \leftarrow c(-1) - c(0) \Rightarrow -c^{(1)} + c^{(2)} - c^{(3)} + c^{(4)}

11: c^{(3)} \leftarrow (t_3 - t_1)/2 + 2c^{(4)}

12: c^{(2)} \leftarrow t_3 + t_2 - c^{(3)}

```

be 0. If  $2 \mid q$ , we need  $q' \ge 2q$ ; if  $3 \mid q$ , we need  $q' \ge 3q$ ; if  $6 \mid q$ , we need  $q' \ge 6q$ . Note that in the common case where q is a power of two, the inverse of 2 does not exist, and consequently, we need q' = 2q, i.e., an additional bit is needed. In the literature, this is sometimes referenced to Toom–Cook losing bits of precision. In practice, this places constraints on the moduli that can be supported by our multiplication routine. For example, if we would like to use 16-bit coefficients, our Toom-3 implementation only supports  $q \le 2^{15}$ .

Note that the performance of Toom–Cook is in large parts determined by the efficiency of the evaluation and interpolation stages. A straightforward implementation of each row of the Toom evaluation matrix and interpolation matrix will not yield a competitive implementation. Algorithm 1 outlines a more efficient evaluation and interpolation sequence.

**Toom-4.** Similarly, the Toom-Cook can be used to split into more and smaller parts. For example, Toom-4 uses

$$a = y^3 a^{(3)} + y^2 a^{(2)} + y a^{(1)} + a^{(0)}$$

.

It is not hard to see that this requires to evaluate both arguments at seven points as the resulting product contains terms up to  $y^6$ :

$$a \cdot b = c = y^6 a^{(6)} + y^5 a^{(5)} + y^4 a^{(4)} + y^3 a^{(3)} + y^2 a^{(2)} + y a^{(1)} + c^{(0)}$$

.

Common evaluation points for Toom-4 are  $y = \{0, 1, -1, 2, -2, 3, \infty\}$ , i.e.,

$$\begin{bmatrix} a(0) \\ a(1) \\ a(-1) \\ a(2) \\ a(-2) \\ a(3) \\ a(\infty) \end{bmatrix} = \begin{bmatrix} 1 & 0 & 0 & 0 \\ 1 & 1 & 1 & 1 \\ 1 & -1 & 1 & -1 \\ 1 & 2 & 4 & 8 \\ 1 & -2 & 4 & -8 \\ 1 & 3 & 9 & 27 \\ 0 & 0 & 0 & 1 \end{bmatrix} \begin{bmatrix} a^{(0)} \\ a^{(1)} \\ a^{(2)} \\ a^{(3)} \end{bmatrix}.$$

After multiplying  $a(y_i)$  with  $b(y_i)$ , we have

$$\begin{bmatrix} a(0) \cdot b(0) \\ a(1) \cdot b(1) \\ a(-1) \cdot b(-1) \\ a(2) \cdot b(2) \\ a(-2) \cdot b(-2) \\ a(3) \cdot b(3) \\ a(\infty) \cdot b(\infty) \end{bmatrix} = \begin{bmatrix} c(0) \\ c(1) \\ c(-1) \\ c(2) \\ c(-2) \\ c(3) \\ c(\infty) \end{bmatrix} = \begin{bmatrix} 1 & 0 & 0 & 0 & 0 & 0 & 0 & 0 \\ 1 & 1 & 1 & 1 & 1 & 1 & 1 \\ 1 & -1 & 1 & -1 & 1 & -1 & 1 & 1 \\ 1 & 2 & 4 & 8 & 16 & 32 & 64 & 1 \\ 1 & 2 & 4 & 8 & 16 & 32 & 64 & 1 \\ 1 & 2 & 4 & 8 & 16 & -32 & 64 & 1 \\ 1 & 3 & 9 & 27 & 81 & 243 & 729 & 1 \\ 0 & 0 & 0 & 0 & 0 & 0 & 1 \end{bmatrix} \begin{bmatrix} c^{(0)} \\ c^{(1)} \\ c^{(2)} \\ c^{(3)} \\ c^{(4)} \\ c^{(5)} \\ c^{(6)} \end{bmatrix}$$

By inverting the matrix, we obtain the following for interpolation:

$$\begin{bmatrix} c^{(0)} \\ c^{(1)} \\ c^{(2)} \\ c^{(3)} \\ c^{(4)} \\ c^{(5)} \\ c^{(6)} \end{bmatrix} = \begin{bmatrix} 1 & 0 & 0 & 0 & 0 & 0 & 0 \\ -1/3 & 1 & -1/2 & -1/4 & 1/20 & 1/30 & -12 \\ -5/4 & 2/3 & 2/3 & -1/24 & -1/24 & 0 & 4 \\ 5/12 & -7/12 & -1/24 & 7/24 & -1/24 & -1/24 & 15 \\ 1/4 & -1/6 & -1/6 & 1/24 & 1/24 & 0 & -5 \\ -1/12 & 1/12 & 1/24 & -1/24 & -1/120 & 1/120 & -3 \\ 0 & 0 & 0 & 0 & 0 & 1 \end{bmatrix} \begin{bmatrix} c(0) \\ c(1) \\ c(-1) \\ c(2) \\ c(-2) \\ c(3) \\ c(\infty) \end{bmatrix},$$

which requires a much longer evaluation and interpolation sequence. One which proved to yield good performance results in practice is shown in Algorithm 2. Note that we need to divide by  $120 = 5 \cdot 3 \cdot 2^3$  and, consequently, either q needs to be co-prime to 120, such that we can multiply by the inverses, or that we need to perform the smaller multiplications modulo 120q such that no wrap-around happens. If q is a power of two, it suffices to use  $q' = 8 \cdot q$ , i.e., use three extra bits.

**Picking evaluation points.** In previous sections, we have picked points y at which to evaluate the polynomials. Those points seemingly came out of thin air. Indeed, it is possible to pick other points and it is not immediately clear that these points are optimal. It appears natural to always use 0 and  $\infty$  as those are cheap to evaluate at and interpolate from. The other points are arbitrary, and one picks the ones that give the best performance. The points presented in this section are the ones most commonly used in the

#### Algorithm 2 Toom-4 interpolation sequence

```

Input: a = a^{(0)} + a^{(1)}y + a^{(2)}y^2 + a^{(3)}y^3, b = b^{(0)} + b^{(1)}y + b^{(2)}y^2 + b^{(3)}y^3

Output: c = a \cdot b = c^{(0)} + c^{(1)}y + c^{(2)}y^2 + c^{(3)}y^3 + c^{(4)}y^4 + c^{(5)}y^5 + c^{(6)}y^6

\triangleright Evaluate a and b at y = {0, 1, −1, 2, −2, 3, ∞}

2: ... \triangleright Small multiplications \rightarrow c(0), c(\infty), c(1), c(-1), c(2), c(-2), c(3)

3: c^{(0)} \leftarrow c(0) c^{(6)} \leftarrow c(\infty)

▶ Interpolate c

4: t_0 \leftarrow (c(1) + c(-1))/2 - c^{(0)} - c^{(6)}

\triangleright c^{(2)} + c^{(4)}

5: t_1 \leftarrow (c(2) + c(-2) - 2c^{(0)} - 128c^{(6)})/8

6: c^{(4)} \leftarrow (t_1 - t_0)/3 c^{(2)} \leftarrow (t_0 - c^{(4)})

> c^{(2)} + 4c^{(4)}

> c^{(1)} + c^{(3)} + c^{(5)}

7: t_0 \leftarrow (c(1) - c(-1))/2

8: t_1 \leftarrow ((c(2) - c(-2))/4 - t_0)/3

9: t_2 \leftarrow (c(3) - c^{(0)} - 9c^{(2)} - 81c^{(4)} - 729c^{(6)})/3

> c^{(3)} + 5c^{(5)}

c^{(3)} + 5c^{(3)}

> c^{(1)} + 9c^{(3)} + 81c^{(5)}

10: t_2 \leftarrow (t_2 - t_0)/8 - t_1

11: c^{(5)} \leftarrow t_2/5 c^{(3)} \leftarrow t_1 - t_2 c^{(1)} \leftarrow t_0 - c^{(3)} - c^{(5)}

> 5c^{(5)}

```

literature in the context of lattice-based cryptography, but other choices are possible.