# Fast and Clean: Auditable high-performance assembly via constraint solving

Amin Abdulrahman<sup>1,2</sup>, Hanno Becker<sup>3</sup>, Matthias J. Kannwischer<sup>4</sup> and Fabien Klein<sup>5</sup>

<sup>1</sup> Ruhr University Bochum, Germany amin.abdulrahman@mpi-sp.org

<sup>2</sup> Max Planck Institute for Security and Privacy, Bochum, Germany

<sup>3</sup> Automated Reasoning Group, Amazon Web Services, Cambridge, United Kingdom<sup>‡</sup>

beckphan@amazon.co.uk

<sup>4</sup> Quantum Safe Migration Center, Chelpis Quantum Tech, Taipei, Taiwan<sup>§</sup>

matthias@kannwischer.eu

<sup>5</sup> Arm Limited

fabien.klein@arm.com

**Abstract.** Handwritten assembly is a widely used tool in the development of high-performance cryptography: By providing full control over instruction selection, instruction scheduling, and register allocation, highest performance can be unlocked. On the flip side, developing handwritten assembly is not only time-consuming, but the artifacts produced also tend to be difficult to review and maintain – threatening their suitability for use in practice.

In this work, we present SLOTHY (Super (Lazy) Optimization of Tricky Handwritten assembl<u>Y</u>), a framework for the automated superoptimization of assembly with respect to instruction scheduling, register allocation, and loop optimization (software pipelining): With SLOTHY, the developer controls and focuses on algorithm and instruction selection, providing a readable "base" implementation in assembly, while SLOTHY automatically finds optimal and traceable instruction scheduling and register allocation strategies with respect to a model of the target (micro)architecture.

We demonstrate the flexibility of SLOTHY by instantiating it with models of the Cortex-M55, Cortex-M85, Cortex-A55 and Cortex-A72 microarchitectures, implementing the Armv8.1-M+Helium and AArch64+Neon architectures. We use the resulting tools to optimize three workloads: First, for Cortex-M55 and Cortex-M85, a radix-4 complex Fast Fourier Transform (FFT) in fixed-point and floating-point arithmetic, fundamental in Digital Signal Processing. Second, on Cortex-M55, Cortex-M85, Cortex-A55 and Cortex-A72, the instances of the Number Theoretic Transform (NTT) underlying CRYSTALS-Kyber and CRYSTALS-Dilithium, two recently announced winners of the NIST Post-Quantum Cryptography standardization project. Third, for Cortex-A55, the scalar multiplication for the elliptic curve key exchange X25519. The SLOTHY-optimized code matches or beats the performance of prior art in all cases, while maintaining compactness and readability.

$\begin{tabular}{lll} \textbf{Keywords:} & Superoptimization & Constraint Solving & Cryptography & Post-Quantum Cryptography & Armv8.1-M & AArch64 & Helium & Neon & Kyber & Dilithium & X25519 & Fast Fourier Transform & FFT & Number Theoretic Transform & NTT & Software Pipelining & Google OR-Tools \\ \end{tabular}$

<sup>&</sup>lt;sup>‡</sup>This work was done while the author was at Arm Research.

<sup>§</sup>This work was done while the author was at Academia Sinica.

# 1 Introduction

Software optimization involves trade-offs, some affecting traditional metrics such as performance, code-size, and memory usage, others affecting softer metrics such as readability, maintainability, and verifiability. While the initial study of algorithms and implementations for nascent computational problems typically focuses on the traditional metrics, it is the softer metrics that are equally important as implementations leave their home of research and step into the "real world". Post-Quantum Cryptography (PQC) is a timely example: Implementations of PQC have been studied extensively in the past years for their core performance metrics. However, now that draft standards for the first winners of NIST's Post-Quantum Cryptography standardization project [NIS16] are available [NIS23b, NIS23a, NIS23c] and the use of PQC becomes increasingly urgent, the soft metrics become central: Are implementations understandable, maintainable, verifiable? This work aims to facilitate the transition of high-performance PQC implementations from research into practice.

At the architectural and microarchitectural level, implementors often face the choice between handwritten assembly and compiled languages. This choice is a trade-off: While handwritten assembly typically yields highest performance, it also tends to be time-consuming to develop and difficult to read and maintain. Conversely, writing software in compiled languages, such as C, offers fast development times as well as clean and portable code, but performance is generally worse than that of handwritten assembly. The reason is simple: The use of compiled languages leaves a number of tasks to the compiler which are too complex for compilers to solve optimally, especially within their limited time budget. Solving those complex tasks manually is thus an opportunity for performance, but also a risk for laborious development with inscrutable results.

Among the tasks taken care of by compilers are the following: First, identifying how the semantics of terms in the source language can be expressed through the instructions of the target machine language. For example, a C developer may simply write a%b for the reduction of a modulo b, but finding efficient algorithms to compute such modular reductions and expressing them in terms of the target architecture, are non-trivial questions left to the compiler (developers) this way. Second, once this *instruction selection* step is done, the tasks of register allocation and instruction scheduling. Continuing the example of modular reduction: An implementation of modular reduction via (say) Barrett reduction might have been provided for the target architecture, but if numerous such reductions need to be orchestrated alongside other code, finding appropriate instructions scheduling and register allocation strategies is a difficult problem on its own.

Two popular approaches addressing the dilemma of choosing between handwritten assembly and compiled languages are the following: First, inline assembly allows developers to force the use of a particular instruction sequence while leaving the allocation of input/output registers to the compiler. Second, extensions like the Arm C Language Extension (ACLE) use *intrinsincs* to expose architectural details such as SIMD instructions into higher level languages. Both approaches give the programmer some control over instruction selection, but leave scheduling and/or register allocation to the compiler.

Another approach is to replace or augment off-the-shelf compilation with custom tooling handling some of instruction selection, instruction scheduling or register allocation, or related tasks. For example, the <code>qhasm</code> tool [Ber] provides a customizable syntax frontend for assembly language which leaves control over instruction selection and scheduling in the hands of the developer, but takes care of register allocation. This allows the developer to effectively still write assembly, but using symbolic registers and a custom syntax, thereby achieving artifacts that can be more readable and maintainable than raw assembly. However, instruction scheduling remaining in the hands of the programmer is, again, both an opportunity for performance and an impediment to readability and fast development.

In this work, we propose and implement a framework for assembly development in

which the developer stays in full control over instruction selection, while instruction scheduling, register allocation and also loop optimization (aka software pipelining) are automated based on models of the underlying architecture and microarchitecture. This way, manual work is restricted to the most difficult and creative aspect of selecting algorithms and mapping them to the target architecture. Moreover, since register allocation and scheduling are automated, the developer can write "clean" code emphasizing the logic of the computation and using symbolic register names, thereby achieving reviewable and maintainable code artifacts. Moreover, formal verification can be decomposed into separately verifying the correctness of the "clean" base code, and the semantics-preservation of the transformation underlying the optimized scheduling and register allocation. Finally, since the microarchitectural model is flexible, our approach allows porting code to new microarchitectures with little effort.

Compared with traditional compilation, our approach is less reliant on fast but approximative algorithms, and is instead based on superoptimization in search for *optimal* solutions: More precisely, we use constraint solving to express the simultaneous optimization of register allocation, instruction scheduling, and software pipelining as a constraint satisfaction problem which is then passed to an external solver.

#### **Contributions.** Our contributions are fourfold:

- 1. We describe SLOTHY (Super (Lazy) Optimization of Tricky Handwritten assembly), a (micro)architecture agnostic approach to modelling the simultaneous assembly-level optimization of register allocation, instruction ordering and software pipelining as a constraint satisfaction problem.

- 2. We develop instantiations of SLOTHY for multiple architectures and microarchitectures: (a) A model of the Armv8.1-M+Helium architecture and the Cortex-M55 + Cortex-M85 microarchitectures implementing it, (b) a model of the AArch64+Neon architecture and the Cortex-A55 + Cortex-A72 microarchitectures implementing it.

- 3. We provide an implementation slothy of SLOTHY based on CP-SAT from Google OR-Tools. As a development tool, slothy converts "clean" and microarchitecture-agnostic input assembly (using e.g. symbolic registers and macros for readability) into microarchitecture-specific high-performance assembly. slothy's output is not only fast, but also compact and auditable: Loops can be optimized without unrolling, and we outline how trace annotations can support manual or automatic checks of the equivalence of input and output, without having to trust SLOTHY itself.

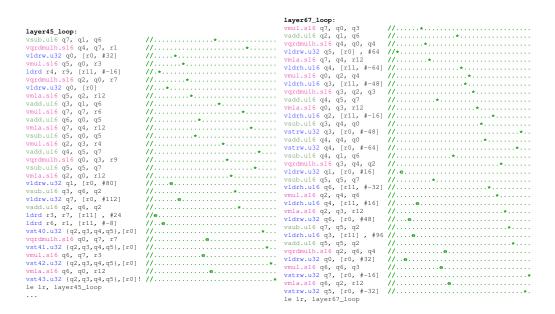

- 4. We demonstrate the practicality of SLOTHY by optimizing multiple real-world workloads from Digital Signal Processing and cryptography: (a) on Cortex-M55 and Cortex-M85, a radix-4 complex Fast Fourier Transform (FFT) in fixed-point and floating-point arithmetic, (b) on Cortex-M55, Cortex-M85, Cortex-A55 and Cortex-A72, instances of the Number Theoretic Transform (NTT) underlying the PQ key encapsulation and signature schemes CRYSTALS-Kyber and CRYSTALS-Dilithium (to be standardized as ML-KEM and ML-DSA, respectively [NIS23a, NIS23b]), and (c) on Cortex-A55, the X25519 scalar multiplication. In all cases, slothy transforms "clean" base implementations into high-performance implementations that match or outperform prior microarchitecture-specific handwritten assembly, while also maintaining compactness, auditability, and portability to further microarchitectures.

#### **Future work.** There are multiple avenues of future work.

First, we encourage research in the application of SLOTHY to other (micro)architectures and workloads. In the context of post-quantum cryptography, for example, we do deliberately not build complete implementations of CRYSTALS-Kyber and CRYSTALS-Dilithium.

We believe that doing so, under consideration of the numerous implementation techniques available, would make for an attractive piece of follow-up research. See also Section 6.4.

Second, the soundness & trust story for SLOTHY should be further elaborated: We argue in Section 5.2 that neither SLOTHY nor slothy need to be trusted to verify the optimizations they yield, and outline and partially implement a verification strategy. However, developing that strategy into a full automated verification of the results of SLOTHY would require further research. We believe that the tooling developed in  $[BGL^+20]$  may be adaptable for this purpose.

Third, the integration of SLOTHY with other compilation and/or superoptimization tooling could be considered: For example, the LLVM infrastructure includes mechanisms to parse code into computational flow graphs and to encode microarchitectural details—one could aim to share those with slothy. Going one step further, SLOTHY could be made an optional optimization pass (enabled, for example, through a suitable #pragma) during a compiler's code-generation phase, after instruction selection.

**Structure.** In Section 3, we discuss various preliminaries on (micro)architecture, compilation and combinatorial optimization. In Section 4, which is the heart of this paper, we describe our approach SLOTHY to the simultaneous optimization of register allocation, instruction scheduling and software pipelining via constraint solving. In Section 6, we discuss our instantiations of SLOTHY for Cortex-M55, Cortex-M85 (both Armv8.1-M+Helium) and Cortex-A55 and Cortex-A72 (both AArch64+Neon). Section 7 discusses our CP-SAT-based implementation of SLOTHY in Python, and illustrates in a toy example how we see it being used as a development tool. Finally, in Sections 8.1, 8.2, 8.3 and 8.4, we work through the examples of the Fast Fourier Transform, Number Theoretic Transform and X25519. We conclude with Section 9 containing some reflections and outlook.

**Software.** SLOTHY and its instantiations for the aforementioned microarchitectures are available under MIT license on https://github.com/slothy-optimizer/slothy.

# 2 Related work

The term *superoptimization* was introduced in [Mas87] as finding "the shortest program that computes the same function as the source program by doing an exhaustive search over all possible programs". Here, we use it more liberally for any approach to software optimization that applies a form of deep program search to find programs that improve upon the results of traditional compilation techniques in terms of size and/or performance.

**Synthesizing vs. fixed-instruction superoptimization.** Following [Emb15, Section 11], one can broadly distinguish two separate kinds of superoptimizers: First, synthesizing superoptimizers ("DAG superoptimizer" in [Emb15]): Those search for optimal (e.g. short) sequences of assembly expressing a given, typically loop-free, piece of functionality. Second, fixed-instruction superoptimizers ("lowering superoptimizer" in [Emb15]): Those take the choice of instructions as a given and search for an optimal scheduling, register allocation and potentially software pipelining strategy.

Synthesizing superoptimization is a long-standing and active field of research [JNR02, SCC<sup>+</sup>17, SSA13, SSA14, SSCA13, BDK<sup>+</sup>16]. Most recently, [KEG<sup>+</sup>23] describes the architecture and implementation for a superoptimizer synthesizing formally verified high-performance cryptographic code for x86-64 from high-level specifications, and [MMZ<sup>+</sup>23] applies reinforcement learning to synthesize a novel high-performance sorting kernel. Fixed-instruction superoptimization, in turn, has seen a flurry of research primarily in the 1990's [GN92, WGB94, Alt95, GAG96, Sto96, GW96, AGG98, KL99, KW98, NG07], but

appears somewhat dormant since. Attempting a renaissance, this work firmly belongs to the realm of fixed-instruction superoptimization.

Reconsidering fixed-instruction superoptimization. There are multiple reasons to reconsider fixed-instruction superoptimization with this work. First, despite the availability of highly out-of-order CPUs, the class of microarchitectures that are highly sensitive to instruction scheduling remains large to-date, encompassing embedded CPUs, in-order application CPUs, domain-specific accelerators, and (as we show) even some out-of-order CPUs. For those microarchitectures, fixed-instruction superoptimization is a complex and impactful problem worth study in its own right.

Second, in the realm of cryptographic engineering – which is the central theme of the examples studied here – fine-grained control over instructions and instruction patterns is often necessary to avoid side-channels, and that control is at risk of being lost with synthesizing superoptimization: E.g., synthesis might undo masking techniques or switch to instructions with data-dependent timing. SLOTHY, in turn, keeps the developer in control over the choice of instructions and the constraints by which code may be rearranged.

Third, when restricting to fixed-instruction superoptimization, the use of *complete* search procedures by way of constraint-solving becomes feasible. Synthesizing superoptimizers, in turn, typically use incomplete search procedures such as stochastic search [SSA13], genetic improvement [BGL<sup>+</sup>20, KEG<sup>+</sup>23], or machine-learning based synthesis [MMZ<sup>+</sup>23].

Comparison to Recent Work. A fair quantitative comparison between our fixed-instruction superoptimization and recent synthesizing superoptimization is not readily possible due to the different target architectures: While we focus on M- and A-class Arm CPUs here, [SCC $^+$ 17, SSA13, BGL $^+$ 20, KEG $^+$ 23, MMZ $^+$ 23] focus on CPUs implementing the x86-64 architecture. It would be interesting to see how synthesizing superoptimization fares in comparison with SLOTHY when implemented on the same (micro)architecture.

The SLOTHY approach to fixed-instruction superoptimization presently requires a handwritten model of the target microarchitecture (see Section 6), and thereby differs from recent synthesizing superoptimizers: E.g., [SCC<sup>+</sup>17] operates on the level of the LLVM IR and is not target specific, [SSA13] uses simplified cost-models for rapid evaluation of candidate optimizations, while [BGL<sup>+</sup>20, KEG<sup>+</sup>23] simply run candidate optimizations on the target. Finally, [MMZ<sup>+</sup>23] uses a pretrained latency estimator. We believe that a detailed microarchitectural model — either handwritten, auto-generated, or even learned — is essential to unlock highest performance for the CPUs considered in this paper.

The development flow advocated for here is close to [BGL<sup>+</sup>20]: They propose that developers write a "clean" and an optimized piece of assembly, the former being amenable to formal verification and the connection between the two verified via "verified transformers", leveraging hints from the developer. They also study the use of genetic improvement to automate optimization, similar to [KEG<sup>+</sup>23]. While so far specific to x86-64, [BGL<sup>+</sup>20] may be adaptable to handle the verification of the transformations found by SLOTHY, based on the "hints" SLOTHY produces; see Section 5.2.

**Fixed-instruction Superoptimization via Constraint-Solving.** As mentioned above, the use of constraint programming (and Integer Linear Programming (ILP) in particular) for fixed-instruction superoptimization is not new, yet the field appears dormant after [GN92, WGB94, Alt95, GAG96, Sto96, GW96, AGG98, KL99, KW98, NG07]. The approach presented here was developed independently, and is, to the best of our knowledge, significantly different from prior art, as we now explain.

First, our approach to software pipelining rests on the simplifying constraint that only neighbouring iterations may overlap. In contrast, prior ILP-formulations for software pipelining, as well as heuristic software pipelining algorithms, typically allow arbitrarily

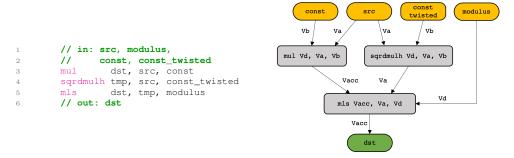

Figure 1: Left: Barrett multiplication [BHK<sup>+</sup>21] in Neon (lane widths elided). Right: The underlying computational flow graph.

far iterations to overlap. We have so far found our restriction insignificant in the medium to large loops that we mainly consider in this paper, while for small loops, modest loop unrolling (e.g.  $2\times-4\times$ ) increases the effective overlapping distance between iterations.

Second, our modeling approach includes *concrete* register allocation, that is, solutions to the constraint model include assignments of registers to instruction arguments. Prior ILP-formulations, in turn, seem to focus on bounds on the total number of registers used. Since our target architectures include numerous instruction-specific register constraints (such as requirements for high/low/distinct/consecutive registers), integrating concrete register allocation into our model is essential for it to apply to those architectures.

Third, the presentation-style of our constraint model has a very different "flavour" compared to prior ILP-formulations, as it stays at the level of boolean, integer and interval variables to reduce the optimization problem at hand to a form of flexible job shop problem.

**Declarative vs. Algorithmic optimization.** When comparing our work to scheduling and software pipelining algorithms used by compilers, we emphasize that our approach is *declarative*, not *algorithmic*: By way of the constraint model developed in this work, it is described *what* an ideal, optimized code would look like, but not *how* it can be computed: It is left to the underlying solver to synthesize a solution or find that there is none. As such, our approach is fundamentally different from, and not relying on, the various algorithmic (often heuristic) approaches for scheduling and software pipelining employed by compilers, such as iterative modulo scheduling or swing modulo scheduling [Rau94, LGAV96].

# 3 Background

#### 3.1 Compilation terms & techniques

Computational flow graphs. A computational flow graph (CFG) represents a computation as a labelled directed graph, with nodes corresponding to computation steps and labelled edges indicating how outputs of one step are used as inputs of others. In this paper, we exclusively work with CFGs representing computations in assembly, with nodes corresponding to the instructions of the architecture under consideration. Inputs and outputs to the entire computation are represented as 'virtual' instruction nodes without inputs and outputs, respectively. Figure 1 provides an example. Note that the ordering of instructions and the use of registers are forgotten when lifting assembly into a CFG. The reverse process is called lowering and is essential in the code generation phase of compilers.

**Phase ordering problem.** Lowering a CFG into assembly requires *instruction scheduling* and *register allocation*: Instruction scheduling assigns a linear order to instructions —

```

1 vldrw.u32

1 vldrw.u32

q0, [inA]

q0, [inA]

1 vldrw.u32

vadd.u32

2 vadd.u32

2 vadd.u32

q0, q0, q0

q0, q0, q0

3 vldrw.u32

wadd 1132

q0, q0, q0

3 vadd.u32

q0, q0, q0

[inB]

4 vstrw.u32

4 vstrw.u32

4 vadd.u32

q0, [inA]

q0, [inA]

q0, q0, q0

5 vldrw.u32

q0, [inB]

5 vldrw.u32

q1, [inB]

5 vmul.u32

q1, q1, q1

6 vmul.u32

vmul.u32

6 vstrw.u32

q0, q0, q0

q1, q1, q1

q1, q1, q1

q0, [inA]

vmul.u32

vmul.u32

q0, q0, q0

vmul.u32

q1, q1, q1

vstrw.u32

vstrw.u32

```

Listing 1: Left: Two logically independent code paths using the same register. Middle: Register renaming to separate register usage and enable interleaving. Right: Interleaving.

a labelling of the CFG's nodes. Register allocation assigns architectural registers to instruction inputs/outputs — a labelling of the CFG's edges. Instruction scheduling and register allocation influence each other, as the choice of scheduling restricts the set of valid register allocations, and vice versa: An instruction must not overwrite a register (an aspect of register allocation) if that instruction is placed in between a producer and consumer of said register (an aspect of scheduling). The relation and ordering between instruction scheduling and register allocation is called the phase ordering problem.

Software pipelining. Software pipelining [Lam88, RG81] is a software optimization technique whereby multiple iterations of a loop are interleaved to create instruction level parallelism and thereby facilitate execution on the underlying microarchitecture. Popular approaches are iterative modulo scheduling [Rau94] and swing modulo scheduling [LGAV96]. While originally devised for Very Long Instruction Word (VLIW) processors, software pipelining is well-known also for classical microarchitectures: When the execution of one loop iteration cannot progress due to latency constraints or lack of availability of functional units, instructions from the next iteration(s) may be pulled forward to fill the gaps. This is conceptually similar to how out-of-order microarchitectures reorder instructions during execution (explained below), but explicit software pipelining may still be beneficial even for such microarchitectures.

Software pipelining puts pressure on the register file since iterations may only be interleaved once there is no collision in their register use. In an out-of-order microarchitecture, this is a consequence of register renaming assigning a fresh physical register to each instruction output, thereby benefiting from a physical register file that's larger than the architectural register file. Software pipelining, however, has to perform manual register renaming within the *architectural* register file, which can be challenging. See Listing 1 for a toy example of an interleaving opportunity created through register renaming.

# 3.2 (Micro)architecture

While the ideas behind SLOTHY are (micro)architecture independent, a basic knowledge of CPU (micro)architecture in general, and the Arm architecture in particular, is necessary to appreciate the concrete examples discussed in this paper. We provide a brief overview.

# 3.2.1 Microarchitecture 1-1

This section provides a minimal mental model of instruction execution, formulated in a somewhat non-standard way via computational flow graphs. For thorough introduction to microarchitecture design, we refer to [TA16].

An instruction's life in stages. All processors considered here execute instructions in a series of stages called pipeline. At the start of the pipeline, instructions are fetched from memory, decoded and have their arguments determined. The processor then tracks

the availability of an instruction's arguments, and when ready, *issues* it to an *execution* unit: For example, arithmetic operations are typically sent to an arithmetic logical unit (ALU). When the instruction's results are ready, they are written back to the register file or forwarded to instructions waiting for them.

**Execution order.** While the journey of an individual instruction through the pipeline is sequential, the above does not imply an ordering between *different* instructions with respect to their time of issuing and execution. Instead, in the language of computational flow graphs (CFG), we can (conceptually) think of the processor as conducting an ad-hoc lifting of the instruction stream into a CFG and then dynamically lowering it. The distinction of *in-order* vs. *out-of-order* execution is about how this lowering is determined.

**In-order execution.** Recall that lowering a CFG requires assigning output registers and an order to instructions. In-order execution is the simplest possible approach here: The issue order is the program order, and the physical registers used by an instruction directly correspond to the architectural registers used in the assembly.

**Out-of-order execution.** Out-of-order execution lowers the instruction stream's CFG by availability: An instruction is issued when arguments and execution unit(s) are available. If multiple instructions are ready in this sense, typically the earliest instruction with respect to the original program order is issued. Instructions "waiting" in the CFG are typically realized via multiple *issue queues* connecting instructions to the units that will execute them. An instruction entering an issue queue is called its *dispatch stage*, and the part of the pipeline prior to dispatch is called the *frontend*; it is typically in-order, and in our mental model corresponds to the dynamic construction of the CFG.

**Register renaming.** In out-of-order execution, the physical registers used by instructions are decoupled from the architectural registers used in the original assembly — the latter are merely dependency labels. Instead, an instruction is assigned "fresh" physical registers for their outputs at the *register renaming* stage prior to dispatch. In particular, in an out-of-order CPU, the left and middle snippets from Listing 1 are identical after register renaming, enabling an out-of-order execution as in the right snippet. Without register renaming, out-of-order execution would be severely limited by the resulting register hazards.

## 3.2.2 M-Profile Vector Extension / Helium

The M-Profile Vector Extension (MVE) is a Single Instruction Multiple Data (SIMD) extension that was introduced as part of the Armv8.1-M architecture [Armf]. Its primary goal is to enable higher performance for signal processing and machine learning applications.

MVE is also referred to as Arm<sup>®</sup> Helium<sup>™</sup> technology, in alignment with the Arm<sup>®</sup> Neon<sup>™</sup> technology architecture extension for A-profile processors [Arma, Section C.3.5], or Neon for short. However, despite the similarity in name, Helium is a new ground-up architecture designed specifically for the tight area/power constraints of the embedded market. We refer to [BBMK<sup>+</sup>21, Armg, Arms, Armt] for introductions to Armv8.1-M+Helium and to the reference manual [Armf] for the details.

What is most important about Helium for the sake of this work is how it carefully introduces software constraints to lower hardware complexity and thereby retain suitability for embedded microcontrollers: Most notably, instruction overlapping and the compact vector register file of  $8 \times 128$ -bit vector registers.

First, instruction overlapping allows to achieve up to  $2\times$  performance with the same execution resources compared to non-overlapping, single-issued execution. However, it requires instructions to be scheduled in such a way that they run on different functional

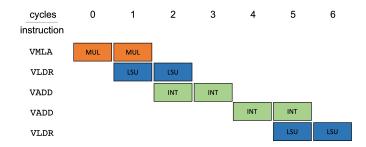

Figure 2: Illustration of instruction overlapping for instructions relying on separate functional units.

```

vldrw.u32

q0, [inA]

1 vldrw.u32 q1, [inB], #16

//-

vldrw.u32

[inA,

#16]

vldrw.u32 q2, [inA, #16]

q1,

vldrw.u32

q2,

[inA, #32]

vmulh.u32

q7, q2, q1

vldrw.u32

[inB],

#16

//-

4 vldrw.u32 q4, [inA,

#32]

vmulh.u32

q0,

q0, q7

5 vadd.u32 q7, q7, q7

vmulh.u32

q1, q1, q7

6 vmulh.u32 q6, q4, q1

7 vadd.u32

vmulh.u32

α2.

a2. a7

a4. a7.

vadd.u32

8 vldrw.u32 q2, [inA]

q0, q0, q0

vadd.u32

q0, q0, q7

9 vadd.u32

q7, q6, q6

vadd.u32

10 vmulh.u32

q1, q1

11 vadd.u32

q1,

11 vadd.u32

12 vstrw.u32 q4, [inA,

12 vadd.u32

q2,

q2, q2

13 vadd.u32

13 vadd.u32

q2,

q2, q7

q4, q6, q6

14 vstrw.u32 q7, [inA,

14 vstrw.u32

[inA, #16]

#321

q1,

vstrw.u32

q2,

q7, q4, q1

16 vstrw.u32 q7,

vstrw.u32

```

Listing 2: Left: Poorly written snippet of Helium assembly with little potential for instruction overlapping. Right: Improved scheduling + register allocation. An //- annotation indicates a structural hazard preventing instruction overlapping.

units and are therefore amenable to overlapping. Figure 2 provides an illustration, assuming an implementation of Helium where each vector instruction takes two cycles ("dual beat implementation") and where there are separate functional units for vector load/store (LSU), integer addition/logical operations (INT), and multiply operations (MUL) — the Cortex-M55 CPU is an example. We can see how the first instructions overlap, leading to high resource utilization, but how the consecutive pair of VADD stalls the pipeline. Typically, there is flexibility in the instruction scheduling, so that good interleaving of different instruction types is possible. For example, Listing 2 shows two versions of the same piece of (meaningless) Helium assembly, one poorly scheduled, making little use of instruction overlapping, and another with a good mix of instructions, facilitating overlapping.

Second, the compact vector register file reduces the cost of CPUs implementing Helium, but requires developers or compilers to manage register usage very carefully, and balance it with the general purpose register file through the use of scalar-vector instructions.

A primary goal of this work is to demonstrate how to automate the process of solving the software constraints posed by Helium through constraint solving.

Implementations. Armv8.1-M+Helium is implemented by the Cortex-M55 and Cortex-M85 CPUs, both of which we will be optimizing for in this paper. The Cortex-M55 is the first processor supporting Armv8.1-M+Helium, and considered a mid-range implementation in Arm's M-profile line. The Cortex-M85 processor, in turn, is considered a high-end implementation, which in addition to support for Helium also offers extensive dual-issuing capabilities. More relevant microarchitectural details will be discussed in Section 6.2.

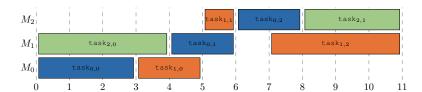

Figure 3: An instance of the job shop problem.  $task_{i,j}$  denotes task j of job i.

#### 3.2.3 AArch64+Neon

We will also be optimizing workloads for the Cortex-A55 and Cortex-A72 CPUs. Those CPUs belong to the A-profile of the Arm architecture and implement the AArch64 64-bit execution state, which was introduced in Armv8-A [Armb] and is also used in the Armv8-R and Armv9-A architectures. AArch64 offers 31 general purpose registers of 64-bit each, as well as 32 vector registers of 128-bit each, which are operated on by the A64 instruction set including the Neon SIMD vector extension (there are also the SVE and SVE2 vector extensions operating on vectors of flexible width of up to 2048-bits, but we will not consider those in this paper). For an introduction to AArch64+Neon, we refer the reader to [Armp, Armb]. In this paper, we will be optimizing for the Cortex-A55 and Cortex-A72 CPUs: The Cortex-A55 CPU is an efficiency-focused, in-order implementation of AArch64+Neon with extensive dual-issuing capabilities, while the Cortex-A72 CPU is a high performance, out-of-order core — more details will be discussed in Section 6.3.

# 3.3 Combinatorial optimization

(Flexible) Job shop problem. The job shop problem is a type of scheduling problem: A number of jobs are given which are to be run on a set of machines. Each job consists of a series of tasks to be performed in-order, and for each task there are constraints on the time they take and the machine they must run on. The job shop problem is to find an assignment of the tasks to the machines which optimizes a given measure [ML93], such as the total time taken. For the original job shop problem, each task must run on a fixed machine. For the flexible job shop problem, multiple machines may be suitable for each task [Pin16]. A visualization of an instance of the job shop problem is given in Figure 3.

Google OR-Tools. Google OR-Tools [PF] is a software for combinatorial optimization, tailored at solving problems such as vehicle routing, flows, integer and linear programming, and constraint programming. We find that Google OR-Tools's CP-SAT is well suited to our assembly superoptimization problem, in two ways: First, it's fast. Second, CP-SAT's API allows for the specification of a mix of Boolean, integer, and interval variables, and moreover offers convenient constraints such as non-overlapping for intervals, or mutual difference for a set of integer variables. However, we expect our modeling approach to apply to other constraint solvers as well, and encourage further research and comparison.

# 3.4 The Fourier Transform and its friends

**Introduction.** The Fourier Transform is a transformation for the decomposition of signals into frequency components. It has numerous incarnations — such as Fourier series, the Number Theoretic Transform, and even harmonic analysis on number fields — and a vast range of applications. Simply put, the importance of the Fourier Transform cannot be overstated. Here, we are interested in the discrete Fourier Transform over the complex numbers, which can be viewed as  $\mathbb{C}^n \to \mathbb{C}^n$ ,  $(x_i) \mapsto (\sum_j x_i \zeta_n^{ij})$  where  $\zeta_n = \exp(2\pi i/n)$  is

the standard primitive *n*-th root of unity. Algebraically, this is the same as the splitting by evaluation  $(\text{ev}_{\zeta_n^i}): \mathbb{C}[X]/(X^n-1) \xrightarrow{\cong} \prod_i \mathbb{C}[X]/(X-\zeta_n^i)$ .

Fast Fourier Transform. The Fast Fourier Transform (FFT) is a method for the efficient computation of the Fourier Transform. While the above description of the Fourier Transform suggests quadratic complexity, the FFT splits the computation into a logarithmic number of layers of linear complexity each, giving an overall complexity of  $\mathcal{O}(n \log n)$ . Each FFT layer operates on strided blocks of r data units via so-called butterflies, and r is called the radix of the FFT. Common choices are radix-2 and radix-4. Efficient implementations of the FFT are an essential component of any Digital Signal Processing (DSP) library, with complex numbers presented in either floating point or fixed point format.

In the realm of Post-Quantum Cryptography, the FFT is of interest for the fast Fourier sampling of the digital signature scheme FALCON [PFK<sup>+</sup>22], selected for standardization by NIST in 2022 [NIS16].

Number Theoretic Transform. The Number Theoretic Transform (NTT) is a variant of the Fourier Transform that's defined over the integers rather than the complex numbers: While the latter splits  $\mathbb{C}[X]/(X^n-1)$  as  $\prod_i \mathbb{C}[X]/(X-\zeta_n^i)$  for the complex n-th root of unity  $\zeta_n = \exp(2\pi i/n)$ , the NTT splits a modular polynomial ring  $\mathbb{F}_q[X]/(X^n-1)$  as  $\prod_i \mathbb{F}_q[X]/(X-\omega^i)$ , for  $\omega \in \mathbb{F}_q$  a modular primitive n-th root of unity, that is,  $\omega^n = 1$  modulo q, but  $\omega^i \neq 1$  modulo q for all i < n.

Structurally, the NTT is the same as the Fourier Transform, and in particular can be implemented in  $\mathcal{O}(n\log n)$  time through a variant of the Fast Fourier Transform. However, the underlying coefficient arithmetic relies on modular integer arithmetic rather than floating point or fixed point arithmetic.

Fast implementations of the Number Theoretic Transform are essential for high performance implementations of post-quantum cryptography, which use the NTT for polynomial multiplication (using the analogue of the convolution theorem in digital signal processing). The recently designated winners Kyber [SAB+22] and Dilithium [LDK+22] of the NIST Post-Quantum Cryptography standardization project [NIS16] both rely on the NTT. In this work, we target the NTTs for these schemes. Kyber uses a 7-layer incomplete 16-bit NTT with n=256 and q=3329, while Dilithium uses an 8-layer complete 32-bit NTT with n=256 and  $q=2^{23}-2^{13}+1$ .

Basic aspects of NTT implementations are the merging of layers (depending on register pressure), the growth of coefficients and insertion of modular reductions (depending on the underlying prime), and the underlying primitive for modular multiplication.

# 4 Assembly optimization as a constraint solving problem

This section, which is the heart of our work, describes  $SLOTHY - \underline{S}uper(\underline{L}azy)$   $\underline{O}ptimization$  of  $\underline{T}ricky$   $\underline{H}andwritten$  assembly — our approach to modeling assembly superoptimization as a constraint solving problem.

#### 4.1 Scope

SLOTHY optimizes instruction scheduling, register allocation and software pipelining. That is, it considers reordering of instructions and change of their use of registers in search for some functionally equivalent but optimally performing variant of the code. Importantly, instruction scheduling and register allocation are considered *simultaneously*, avoiding the phase ordering problem (Section 3.1). In case of a loop, SLOTHY also simultaneously searches for suitable interleavings of iterations. Put differently, SLOTHY retains the (isomorphism class of the) source's computational flow graph.

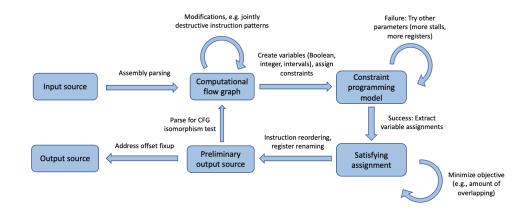

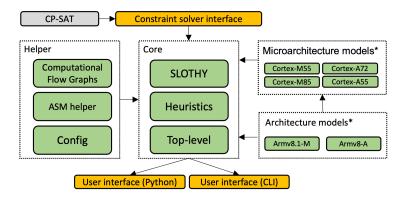

Figure 4: High-level overview of operation of SLOTHY

Figure 4 provides an overview of SLOTHY's operation: First, the input is parsed and converted to a computational flow graph. Next, a constraint model is derived as explained below, and passed to an external solver. Upon success, the (optimal) satisfying assignment found by the solver is converted back into the output source. This source is then subject to some post-processing and self-check before being returned to the caller.

SLOTHY's core does not change instructions except for register renaming. In fact, it has no knowledge of the semantics of instructions beyond their signatures, that is, the number and types of inputs, outputs, and input/outputs. It remains the responsibility of the developer to find ways to express the target computation in terms of the underlying architecture. This is a core design choice of SLOTHY, and we refer to Section 2 for rationale in comparison with synthesizing superoptimization.

Finally, SLOTHY has no built-in notion of memory, only registers. First, reasoning about *dynamic* memory accesses is not possible without awareness of the precise semantics of instructions, which is out of scope of SLOTHY by design, as just discussed. Reasoning about *static* memory accesses, such as stack spills, is possible by modelling static memory locations as special "registers" — this will be explained in Section 4.12.

#### 4.2 Overview

The following sections assume that a piece of assembly to be optimized has been provided and parsed into a computational flow graph (see Section 3). Our goal, then, is to define a constraint model — that is, a set of integer, boolean, and interval variables together with a set of conditions imposed upon them — whose set of solutions captures lowerings of the CFG which are both valid (with respect to the underlying architecture) and of high performance (with respect to the underlying microarchitecture).

Aspects of the model that pertain to validity are discussed in Sections 4.3 and 4.4, while Sections 4.6 and 4.8 discuss microarchitectural performance constraints. Section 4.5 discusses how we incorporate software pipelining into the constraint model, and Sections 4.13, 4.12, 4.7 and 4.14 discuss the modelling of memory, stalls, and optimization objectives.

# 4.3 Correctness/Architecture constraints: Instruction scheduling

Every instruction I of the input source is assigned an integer variable I.pos defining where the instruction is placed in the output code. To get a unique program order in the output, we require  $\{I.pos\}_I$  to be mutually distinct. Further, to maintain functional

correctness, consumers must come after producers: If instruction J consumes output O produced by instruction I — that is, we have an edge I  $\xrightarrow{\circ}$  J in the computational flow graph — then I.pos < J.pos.

# 4.4 Correctness/Architecture constraints: Register Allocation

For every instruction I, every output O of I, and every possible register R that I can use for O, we assign a Boolean variable alloc(I,O,R) indicating whether the instruction I uses register R for the output O. In analogy with the operation of out-of-order microarchitectures, we call this process register renaming. In contrast to out-of-order microarchitectures, however, simultaneous input/output arguments are not subject to register renaming as we need to preserve the architectural constraint that input and output use the same register. For those arguments, we use the notation alloc(I,O,R) as a shorthand for alloc(K,U,R), where K,U is the transitively computed source of O, with U being a pure output (not merely an input/output). For example, if I is an MLA in a {MUL; MLA; ...; MLA} chain and O is the accumulator, we would always go back to the initial MUL which made the choice for which register to use for the accumulator. Finally, note that the input source's choice of registers is irrelevant for register renaming — it is only used initially to construct the computational flow graph from the source.

Multiple constraints need to be satisfied: First, for the uniqueness of register renaming, we require that for fixed I and O, exactly one Boolean variable in  $\{alloc(I,O,R)\}_R$  is set. Second, for functional correctness, we need to express that in between a register being produced and consumed, no other instruction uses the register for register renaming. We model this as a disjointness constraint as follows: First, for any instruction I and any output or input/output O, we add an interval  $[I \stackrel{\circ}{\to}]$  starting at I.pos, and bound its endpoint below by J.pos for any  $I \stackrel{\circ}{\to} J$ , as well as by I.pos + 1 (in case O has no consumers). For any choice of output register R, we then add a copy  $[I \stackrel{\circ}{\to}]_R$  of  $[I \stackrel{\circ}{\to}]$  as a conditional interval constrained by alloc(I,O,R). Functional correctness then requires that for any R, the set of conditional intervals  $\{[I \stackrel{\circ}{\to}]_R\}_{I,O}$  is non-overlapping.

We note that our modelling of register usage is an instance of the flexible job shop problem, with jobs being instructions and "machines" being registers.

**Restricted instructions.** Sometimes there are restrictions on the registers that an instruction can use. Such restrictions often apply to individual arguments (such as requiring even, odd or low-half registers), but there are also more complex cases: For example, the output of VCMUL in Helium must not coincide with an input, and the four (!) vector arguments to the de-interleaving load VLD4x are constrained to the set  $\{Qi,Q(i+1),Q(i+2),Q(i+3)\}$  for i=0,1,2,3,4. Individual restrictions on output arguments are straightforwardly added to the register renaming model by restricting the Boolean variables alloc(I,O,R) accordingly. To model restrictions for multiple register outputs, such as for VLD4x/VST4x, we introduce Booleans for the different choices, constrain that precisely one is set, and then add implications to the respective alloc(I,O,R) variables.

Jointly destructive instruction patterns. The Armv8.1-M+Helium and AArch64+Neon architectures contain instruction patterns where each instruction individually overwrites only part of the destination register, but where the sequence as a whole overwrites it entirely: In AArch64+Neon, for example, the sequence {INS Vi[0].2D, Xj; INV Vi[1].2D, Xk}—writing each of the two 64-bit lanes of a vector in succession — is "jointly destructive" in this sense. In Armv8.1-M+Helium, examples include blocks of VLD4 {0,1,2,3} as well as pairs of VQDMLSDH+VQDMLADHX (jointly performing a complex multiplication in fixed-point arithmetic). By default, the partially destructive components in a jointly destructive instruction pattern would be modelled as having their destination register as

an input/output argument, thereby creating an unnecessary data dependency between the instruction pattern and whatever instruction(s) established the previous value of the destination register(s). This, in turn, limits SLOTHY's renaming and reordering flexibility. To address this, SLOTHY allows architecture specifications to modify instructions within the context of an entire computational flow graph, in particular allowing for the retroactive detection and reclassification of input/output registers as a pure output registers in jointly destructive patterns. We leverage this to detect and mark the destination register in aforementioned patterns as a pure output for the first instruction of the sequence, thereby allowing to reorder it past previous instructions which write to the same register.

# 4.5 Loop interleaving aka Software pipelining

A powerful feature of SLOTHY is software pipelining, that is, interleaving multiple iterations in a loop: Some early instructions, such as initial loads, are moved into the previous iteration, while some late instructions, such as final stores, are deferred to the next iteration. To avoid having to unroll the entire loop, periodicity of code has to be maintained.

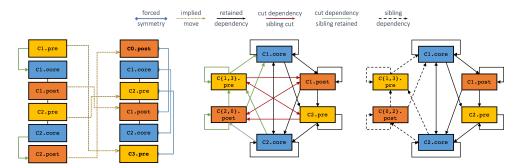

Modeling approach. To begin, for each instruction I we add three Boolean variables I.pre, I.post and I.core, indicating whether I will be an early/late instruction for the previous/next iteration, or whether it stays in its original iteration. Precisely one of {I.pre, I.core, I.post} must be set. For periodicity, we first double the loop body C, say as  $C_1$  and  $C_2$ , and for an instruction I, we denote  $I_1$  and  $I_2$  its copies in  $C_1$  and  $C_2$ , respectively. Note that this duplication is internal only and does not enforce an unrolling of the loop in the final code. We then relate I<sub>1</sub> and I<sub>2</sub> through the following periodicity constraints: First, the choices of I.pre, I.core, I.post and of register allocations must be the same for  $C_1$  and  $C_2$ :  $I_1$ .{pre,core,post}  $\Leftrightarrow I_2$ .{pre,core,post} and  $alloc(I_1, O, R) \Leftrightarrow alloc(I_2, O, R)$  for all  $I \in C$ . Second, "core" instructions are placed exactly n instructions apart, where n is the length of C: If I.core, then  $I_2.pos =$  $I_1.pos + n$ . Third, and perhaps somewhat non-canonically, we force early instructions in  $C_1$  to become early instructions for the next iteration  $C_3$ , and late instructions in  $C_2$  to become late instructions for the previous iteration  $C_0$ . To achieve that, we constrain that for I.pre or I.post, we have  $I_2.pos = I_1.pos - n$  — note the sign! — and "cut" the constraints derived from  $I_1 \xrightarrow{\circ} J_1$  if I.pre, and those derived from  $I_2 \xrightarrow{\circ} J_2$  if J.post. Despite those "cuts", the required constraints are implied by the remaining periodicity constraints, so long as we impose that for  $I_1$  pre and  $I \xrightarrow{\circ} J$ , we have either J.pre or J.core, and similar for J2.post — without this condition, dependencies could be entirely and incorrectly removed by never setting I.core (a previous version of SLOTHY got this wrong). See Figure 5 for an illustration.

**Loop boundary.** We do not model looping instructions such as counter decrements and compare+jumps: First, we don't expect those to have a meaningful impact on the optimization. Second, on Armv8.1-M+Helium in particular, inner iterations in low overhead loops do execute as if the loop had been unrolled, including the potential for instruction overlapping. By modelling the last and first instructions of two successive iterations as adjacent, SLOTHY correctly takes into account the overlapping at the loop boundary.

**Preamble and postamble.** With software pipelining, the first and last iterations have to be treated especially: Concretely, a loop in which some instructions are being pulled into the previous iteration, requires a *preamble* (also called *prologue*) consisting of the early instructions for the first iteration, and a *postamble* (also called *epilogue*), consisting of the non-early instructions of the last iteration. Together, preamble and postamble then account for one full iteration. If both early and late instructions are used, preamble and

Figure 5: Modelling software pipelining in SLOTHY. Left: Illustration of movement of early/core/late parts forced by periodicity. Middle/Right: Illustration of lost and retained dependencies after applying periodicity.

postamble account for two full iterations. In either case, the loop counter needs to be adjusted accordingly.

A downside of the addition of preamble and postamble is an increased code-size. If this is problematic, an alternative is to replace the postamble by a full iteration of the optimized loop body, leaving only the (typically small) preamble as a code-size overhead. This approach is viable if (a) it is safe to read a fixed amount past the input buffer (e.g. because it is padded by the caller), and (b) the preamble does not include store instructions (which can be forced in the SLOTHY model). This approach is used e.g. in [Arme].

# 4.6 Performance/ $\mu$ Arch constraints: Latencies

In this and the following section, we describe how we incorporate performance constraints into our model. For simplicity, we focus on the case of single-issue, in-order microarchitectures first. Superscalar, in-order microarchitectures are discussed in Section 4.9 below, and Section 4.10 comments on out-of-order microarchitectures.

In the context of a single-issue, in-order microarchitecture, an ideal, stall-free program execution would see the execution time difference (in cycles) between two instructions match their distance in program order. We therefore model latencies by requiring that for any  $I \xrightarrow{\circ} J$ , we have  $J.pos \ge I.pos + latency(I \xrightarrow{\circ} J)$ . Note that this supersedes the previously introduced functional correctness constraint  $J.pos \ge I.pos$ . We also note that while  $latency(I \xrightarrow{\circ} J)$  often depends on I only, dedicated forwarding paths provide examples where  $latency(I \xrightarrow{\circ} J)$  may be smaller than the "generic" latency of I: On the Cortex-M55 CPU, for example, vector multiplication instructions typically have a latency of 2 cycles, yet sequences VMULx; VSTRx run stall-free.

# 4.7 Modelling stalls

Performance constraints such as the ones discussed in Section 4.6 may not be satisfiable: Sometimes, stalls are unavoidable. We model stalls by allowing the set of program order positions to have gaps, constraining pos to be an injective map  $\{0,\ldots,|\mathtt{code}|\} \rightarrow \{0,\ldots,|\mathtt{code}|+\mathtt{maxgaps}\}$  rather than a permutation on  $\{0,\ldots,|\mathtt{code}|\}$ . The integer variable maxgaps models the maximum stall "allowance".

We consider two approaches for minimizing maxgaps: In the first approach, we fix maxgaps at model construction time. If the resulting model has a solution, we try again with a smaller value for maxgaps; otherwise, we increase it. Using binary search, a small number of iterations should reveal the minimum stall allowance. In the second approach,

we model maxgaps as an undetermined integer variable that is part of the model, and mark its minimization as the *objective* of the underlying solver, if supported.

Our experiments with CP-SAT did not render either approach generally better than the other: For optimization problems of small or medium complexity, modelling stalls "internally" in the model appears to work well and lead to the optimal solution faster than an "external" binary search. For highly complex models, however, adding further dynamics through the flexible maxgaps could sometimes render the optimization problem infeasible (that is, we would abort the solver prior to having found a solution), while the solver could make progress using an "external" binary search.

# 4.8 Performance/ $\mu$ Arch constraints: Instruction Overlapping

Next, we describe how we model functional units and instruction overlapping. As before, we make the simplifying assumption that the target microarchitecture is single-issue and in-order, leaving generalizations to Section 4.9 and Section 4.10 below.

Instruction overlapping is modeled by assigning to each instruction I a functional unit Unit(I) (depending on the target microarchitecture) and a usage time (in cycles) block(I) capturing for how long I keeps Unit(I) busy. We then demand that for any fixed functional unit U, the set of intervals  $\{[I.pos,I.pos+block(I)) | Unit(I) = U\}_I$  is non-overlapping. This is a straightforward instance of the job shop problem. If an instruction may run on multiple functional units, we create Boolean variables tracking where they actually run, and condition the usage intervals accordingly — that is, we reduce to a flexible job shop problem. On the Cortex-M55 processor, an example for an instruction that can run on multiple functional units is the double vector-to-register move VMOV Ra, Rb, Qn[i], Qn[j].

We highlight that the latency of an instruction may be smaller than its usage time: On Cortex-M55, for example, many vector instructions (e.g. VADD) occupy their functional units for 2 cycles, but have 1 cycle latency: This is possible since instruction overlapping supports data dependencies between the overlapping instructions.

# 4.9 Superscalar microarchitectures

We have so far described our model for single-issue microarchitectures, using a single integer variable I.pos for an instruction's position in program order as well as its (ideal) issue cycle. For in-order, superscalar microarchitectures, we need two separate, yet closely related variables: In addition to I.pos, keeping its meaning as the position of I in program order, we introduce another variable I.cyc for the issue cycle. If N is the maximum number of instructions issued per cycle, we relate I.pos and I.cyc via I.cyc =  $\lfloor \frac{\text{I.pos}}{N} \rfloor$ . Where such ideal issue-rate cannot be achieved, gaps will be left in the program order assignments, as described in Section 4.7. In particular, we note that N may be strictly larger than the issue-rate of the target microarchitecture — the true limit to multi-issuing is enforced through the configuration of functional units (Section 4.8) and microarchitecture-specific constraints capturing which instructions may be issued in the same cycle.

#### 4.10 Out-of-order microarchitectures

A typical out-of-order CPU performs register renaming and instruction reordering in *hardware*. Those also being the core tasks of SLOTHY, one might wonder whether using SLOTHY for out-of-order CPUs is fruitful. Somewhat surprisingly, we found (and show later) that SLOTHY can be useful for some out-of-order CPUs as well, as we explain now.

First, the amount of renaming and reordering a given out-of-order CPU is capable of is bounded, and a trade-off between performance and hardware cost: The number of physical registers available for renaming is fixed, as is the width of the reordering window and the

size of the issue queues. We therefore expect that code which is scheduled in consideration of execution units and latencies, is less likely to hit the limits of the reordering capabilities, and should thus perform better. Concretely, for example, instructions scheduled in consideration of the latencies of their source instructions will have a shorter wait in the issue queue and are therefore less likely to lead to overflows in the latter.

Second, the out-of-order microarchitectures considered here have in-order frontend which takes care of, among other things, register renaming and instruction dispatch to issue queues. If the width of this frontend (for the instruction classes under consideration) is close to the width of the execution backend (for the same class), a constantly high throughput of the former is required for high utilization of the latter — we will look at specific examples later. Moreover, the frontend being in-order, its throughput maximization becomes a scheduling sensitive problem that we can attempt to model in SLOTHY.

## 4.11 Input and output registers

As mentioned in Section 3.1, we model inputs and outputs as special nodes in the computational flow graph, with input nodes not having any inputs, and output nodes not having any outputs. Input nodes are added automatically during CFG construction: If an instruction takes an input argument which has not been written to so far, a new input node is created and a dependency added between that input node and the current instruction. Output nodes, in turn, are created on behalf of the user: SLOTHY cannot know which registers written to by the current program excerpt are actually relevant for the remainder of the program, and which ones are merely temporaries — it's for the user to say. For every output register, we then create an output node dependent on the last instruction that wrote the register. A noteworthy special case is when a register declared as an 'output' is never written to: In this case, a pair of depending input and output nodes is created for that register, thereby preventing other instructions from using the register.

During the construction of the constraint model, input and output nodes are largely treated like ordinary instruction nodes: They have a program order position, input and output dependencies, and contribute to the tracking of register lifetimes and usage. They are only special in that they have their position fixed to the beginning/end of the program, and do not enter *micro*architectural constraints. This uniformity simplifies the model significantly — an earlier version of SLOTHY did not use input and output nodes, and was considerably more complex and error-prone.

## 4.12 Memory, stack and flags

SLOTHY does not have an in-built notion of memory. In our Armv8.1-M+Helium and AArch64+Neon models discussed below, store instructions are modelled as having no output, while load instructions are modelled as having no input except for the address register. This approach is sound if there are no data dependencies through memory within the range of a single SLOTHY optimization, which is the case for the common load-operate-store style loop not relying on the stack as temporary storage.

Where use of the stack is required, the following simple trick can be used: Stack locations can be modelled as "registers" of a separate register type, which are written to and read from via virtual instructions that have the same properties as loads/stores (e.g. in terms of latencies and functional units used). With this approach, which fits into the existing framework of SLOTHY, data dependencies can be tracked across stack spills without having to model linear memory. This approach works more generally for any *static* use of memory. We use it to model the stack in some of the NTT examples as well as the X25519 example discussed in Section 8.4.

A similar trick applies to modelling arithmetic flags: Each such flag can be modelled as a "register" of a dedicated register type, and instructions are marked as depending on or modifying those registers in accordance with their reliance and influence on arithmetic flags. We use this approach to model flags in the X25519 example below.

#### 4.13 Address offset rewrites

A typical loop will modify the base address for the data to be operated on with each iteration: For example, in Helium, data might be loaded via VLDR Qin, [Raddr] for some address register Raddr, and later stored via VSTR Qout, [Raddr], #16, incrementing the address register for the next iteration. Such patterns make deep software pipelining impossible without further modelling of the semantics of the address increments, as there is a data dependency between the final store of one iteration, incrementing the address register, and the initial load for the next iteration. Since SLOTHY does not know about the semantics of instructions beyond their signature and dependencies, it cannot reorder load and store in this situation. With further semantic knowledge, however, one could of course reorder load and store in such situations, leveraging commutativity relations such as VSTR Qa, [Rptr], #16; VLDR Vb, [Rptr]  $\equiv$  VLDR Qb, [Rptr, #16]; VSTR Qa, [Rptr], #16.

We address this problem as follows: To begin, our existing SLOTHY architecture models (see Section 6) do not model address increments, but treat address registers for load/store operations as input-only. This gives SLOTHY the flexibility to freely reorder load/stores and identify deep software pipelining opportunities, but also constitutes a semantic change if a load/store with increment is reordered with another load/store from the same base register. After the optimization, we therefore iterate through pairs of load/stores which depend on the same address register and have been reordered by SLOTHY, and fix up their address offsets, leveraging commutativity relations such as the one above. This works well in the typical case where only one load/store instruction modifies the base register, and where the offers a flexible immediate offset. For pairs of load/store instruction which do not have this flexibility, we forbid their reordering in SLOTHY.

We note that manual address increments via add Raddr, Raddr, #16 do currently still prevent software pipelining in SLOTHY. For loops where such increments can not be realized as pre/post increments, further work on SLOTHY is needed to optimize them.

#### 4.14 Other objectives

Beyond the minimization of stalls, the following are useful objectives: If software pipelining is enabled, it is natural to maximize  $\sum_{\mathtt{I}} \mathtt{I.core}$  — that is, to minimize the amount of interleaving between successive iterations. Second, register usage can be minimized. This is particularly interesting if the code in question does not fit into the register file, and "virtual registers" are used to approximate the amount of stack spilling needed.

# 5 Accuracy, Soundness & Security

#### 5.1 Security

The security of cryptographic code requires dedicated implementation techniques depending on the threat model. For example, constant-time code should not use any branches, memory accesses, or variable-time instructions depending on secret data. Other techniques thwart stronger physical side-channels or fault attacks, such as masking, redundancy, or the specific ordering of instructions and use of registers to avoid pipeline leakage. Where automated code synthesis/optimization is used on cryptographic code, it is thus important to understand if/how it interferes with those techniques.

The implementations studied here are (solely) constant-time, and so are our SLOTHY-optimizations: Since SLOTHY applies fixed-instruction superoptimization, no branches

are introduced, and memory access patterns as well as the specific use of instructions are unaltered. Even if an implementation carefully used a generally variable-time instruction on inputs for which it is known to be constant-time, such as the multiplier on Cortex-M3, then SLOTHY would not lead to insecure use of this instruction (generally, however, it is advisable to stick to instructions *architecturally* guaranteed to have data-independent timing, e.g. via PSTATE.DIT=1 on Arm architectures).

Next, consider SLOTHY's compatibility with stronger side-channel countermeasures: To begin, fixed-instruction superoptimization does not undo masking techniques. Pipeline leakage, in turn, is very sensitive to ordering of instructions and the use of registers [MPW21], the very aspects that SLOTHY can, by default, freely modify. While a detailed study is out of scope for this work, we believe that SLOTHY can overcome even this hurdle: Namely, once developers understand the leakage model and derived implementation principles well enough, they can distill them into SLOTHY constraints and thereby automate their application. As a toy example, [MPW21, Table 6, row ARM<sup>NO</sup>] shows that a specific instance of NXP LPC812M101JDH16 suffers leakage of the Hamming weight of results of neighbouring EOR+LDR and EOR+STR instructions. This can be encoded in SLOTHY with little effort via additional constraints J.pos != I.pos + 1, one per pair (I, J) with (I.type, J.type) ∈ {(EOR, LDR), (EOR, STR)} (similar to the modelling of ST-LDhazards in Section 6.2). This way, SLOTHY will avoid the leaky pattern. Further, if not all such pairs require protection, one can add (functionally transparent) instruction wrappers distinguishing instructions operating on private vs. public data, and limit constraints accordingly. Finally, we similarly expect SLOTHY to be compatible with Spectre/Meltdown countermeasures like [SBG<sup>+</sup>23]: By modelling speculation-stopping instructions such as fences as reordering barriers in the constraint model of SLOTHY (that is, in the language of Section 4, constraining that I.pos < J.pos if either I or J is a speculation barrier and I comes before J in the program input), the mitigations would be upheld.

Overall, we believe that constraint-based fixed-instruction superoptimization is well-placed to act on cryptographic code of various security levels. We see this as an advantage over synthesizing superoptimization, for which the compatibility with secure implementation techniques appears less clear.

## 5.2 Soundness

Soundness means that SLOTHY emits code which is functionally equivalent to the original code. Considering the complexity of the components involved — SLOTHY itself, its implementation, and the underlying constraint solver — it is important to have an approach to establishing soundness that does not require trust in either of those components. In this section, we sketch such an approach, similar to the "verified transformers" of  $[BGL^+20]$  — full elaboration and mechanization, however, is left for future work.

The essential idea is that for fixed-instruction optimizations, correctness should be a consequence of the produced code having a computational flow graph (CFG) isomorphic to that of the input code. Moreover, such an isomorphism can be checked for efficiently once provided with the underlying permutation of the optimization, which is part of the solver's output. In other words, a CFG-preserving optimization step can be verified independently of the constraint modelling approach, the implementation, and the underlying solver. Our SLOTHY implementation performs such a CFG-isomorphism check before emitting the optimized code, but independent verification tooling should be implemented.

There are some non-trivial details to be considered in the above blueprint, which we briefly outline. First, the approach assumes that the semantics of some code is a function of the code's CFG, which requires the CFG to e.g. at least include reads/writes to memory. However, as explained in Section 4.12, SLOTHY does not consider dependencies through memory and elides it from the CFG. This is a valid transformation under the assumption that the code under consideration does indeed not have dependencies through memory,

but nonetheless constitutes a CFG-altering preprocessing prior to the core CFG-preserving optimization that needs independent verification. A similar comment applies to offset rewrites (Section 4.13), which too can be viewed as CFG-altering preprocessing steps.

In summary, we believe that SLOTHY-based optimization is amenable to automated certificate-based verification with SLOTHY and its implementation being untrusted. However, further work is required to elaborate and implement this verification strategy — our own implementation currently only performs the core CFG-isomorphism "selfcheck".

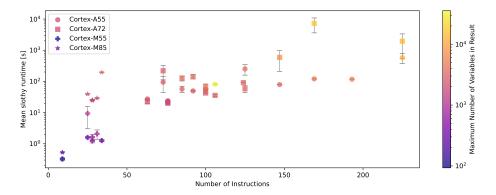

# 5.3 Performance accuracy

The accuracy of SLOTHY's performance expectation depends on the fidelity of the given microarchitectural models. Realistically, those will not be perfectly accurate, but focused on key aspects such as instruction latencies, throughput, execution units, or forwarding paths. Unmodeled microarchitectural aspects may therefore still lead to stalls in code which the (micro)architectural model underlying SLOTHY considers "stall-free". It is therefore important to validate the performance of code produced via SLOTHY by running it on real hardware, and refine the microarchitectural model if necessary.

# 6 (Micro)Architecture models

Section 4 described our (micro)architecture-agnostic framework SLOTHY for assembly optimization via constraint solving. In this section, we discuss our concrete instantiations: We model aspects of the Cortex-M55 and Cortex-M85 CPUs implementing Armv8.1-M+Helium, as well as the Cortex-A55 and Cortex-A72 CPUs implementing AArch64+Neon.

# 6.1 General approach

Architecture modelling. A SLOTHY architecture model has the following main components: First, the set of register types and their associated registers. Register aliases (such as LR being an alias for X30 in AArch64) may be defined, too. Second, the set of instructions required for the workload(s) to be optimized. For every instruction, SLOTHY needs to know about the number of input, output, and input/output registers and their register type. If there are restrictions on which registers can be used, those *must* be modelled, too. Jointly destructive instruction patterns *should* be modelled for best performance. Finally, parsers and writers need to be written for the conversion between assembly and CFGs.

Microarchitecture modelling. A SLOTHY microarchitecture model has the following main components: First, the set of functional units and, for a superscalar architecture, the issue width. Second, the latencies, throughputs, and functional unit of every instruction. Third, special cases and target specific restrictions, a typical example being forwarding paths for common instruction sequences, or issue-slot restrictions.

For in-order microarchitectures, we extract most information from the respective software optimization guides (SWOGs), with further refinement using our own microbenchmarks. For out-of-order microarchitectures, the modelling process is more heuristic: We also gather information regarding the throughputs and latencies from the SWOGs, but experiment with relaxations on the latencies because of out-of-order execution, as well as the modelling of frontend limitations as outlined in Section 4.10.

**Modelling effort.** While the development of (micro)architecture models can be time consuming (see Section 8), it is important to note that it is a one-off effort in the sense that every aspect of the target (micro)architecture needs to be modelled only *once*.

Moreover, models can be developed "lazily", focusing on the instructions required for specific workload(s) first, and gradually expanding the models over time.

#### 6.2 Armv8.1-M+Helium

For an introduction to Armv8.1-M+Helium, we refer back to Section 3.2.2.

Cortex-M55. The Cortex-M55 SWOG [Armk] provides detailed microarchitectural information that can be converted into a SLOTHY model. The most important points are the following: First, Cortex-M55 is a dual-beat implementation of Helium, that is, every Helium instruction runs for two cycles. In terms of the SLOTHY, this means that the throughput of Helium instructions is modelled as 1/2. Second, there are separate Helium execution pipelines for (a) load/store, (b) integer, and (c) floating point / integer multiplication instructions, which are modelled as separate "execution units" in the SLOTHY model. Third, the SWOG details the latencies of Helium instructions, which are reflected in our SLOTHY model, including some latency exceptions because of forwarding paths.

Finally, we constrain the SLOTHY model for Cortex-M55 to forbid patterns of the form VSTx; ?; VLDx, as those patterns do sometimes, depending on address alignment, lead to memory bank conflicts, and thus pipeline stalls. Below, this phenomenon will be referred to as a ST-LD-hazard (the interested reader should consult the SWOG for detailed load/store-pipeline information explaining this).

**Cortex-M85.** We also experiment with a SLOTHY model for the Cortex-M85 CPU. We focus on the microarchitectural aspects related to Helium only: Cortex-M85 brings significant scalar improvements compared to Cortex-M55 because of larger dual-issuing capabilities, but we leave their modelling and use for future work.

In terms of Helium, the Cortex-M85 microarchitecture is overall similar to Cortex-M55, with a few noteworthy differences: First, similar to Cortex-M55, there are separate pipelines for integer and floating-point addition/logical instructions, and for integer and floating-point multiply instructions. Second, loads and stores can overlap (so that e.g. VLDRx; VSTRx; VLDRx; ... can run stall-free), and only some specific sequences such as {ARITH}; VLDx; VSTx; VLDx can lead to stalls — overall, scheduling of loads and stores is more flexible. Third, the Cortex-M85 microarchitecture is designed to be implementable at higher clock-rates than Cortex-M55, which increases some (cycle) latencies compared to Cortex-M55: For example, de-interleaving loads VLD2x and floating-point MACs have a latency of 4 cycles on Cortex-M85. This reinforces the importance of good instruction scheduling, and also explains that, as we will see later (e.g. Section 7.3), the best implementations for Cortex-M55 and for Cortex-M85 may be different.

#### 6.3 AArch64+Neon

**Cortex-A55.** We derived the SLOTHY model for Cortex-A55 from experimentation, the Cortex-A55 SWOG [Armi], and useful observations from [Len19]. Our goal was not to define a fully precise reflection of the Cortex-A55 microarchitecture, but to focus on — and model in *sufficient* detail — the aspects most relevant for our target workloads.

The Cortex-A55 is a superscalar CPU which can dual-issue many pairs of instructions including scalar and 64/128-bit Neon instructions, as well as pairs of 64-bit Neon instructions. Notable exceptions are most pairs of 128-bit Neon instructions, and pairs of multiply-accumulate scalar instructions. We express those characteristics in SLOTHY as follows: First, we add two execution units for 64-bit vector operations, but mark 128-bit vector instructions as occupying both. Second, we model two scalar execution units and mark one as capable of multiple-accumulate instructions; this is a deviation from the SWOG showing 3 scalar pipelines, but our model is sufficient for our purposes. Third, we

model separate execution units for load/store operations. Finally, we incorporate issue-slot restrictions, an important example being that most 128-bit Neon instructions are only issued on slot 0. Latencies and throughputs are modelled as provided in the SWOG, with occasional changes as suggested by our microbenchmarks. We also model the forwarding paths for scalar and Neon multiply-accumulate sequences in SLOTHY, including their additional constraints identified and highlighted in [Len19].

**Cortex-A72.** In contrast to the Cortex-M55, Cortex-M85 and Cortex-A55 microarchitectures considered above, the Cortex-A72 is a triple-issue, *out-of-order* microarchitecture. We refer to Section 4.10 for the general discussion of the uses SLOTHY can have in this context. For Cortex-A72, our SLOTHY model captures a somewhat heuristic combination of frontend and backend constraints, as we explain now.